- Verilog HDL中,有兩種過程賦值方式,即阻塞賦值(blocking)和非阻塞賦值(nonblocking)。阻塞賦值執行時,RHS(right hand statement)估值與更新LHS(left hand statement)值一次執行完成,計算完畢,立即更新。在執行時

- 關鍵字:

Verilog HDL 阻塞屬性

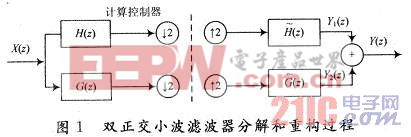

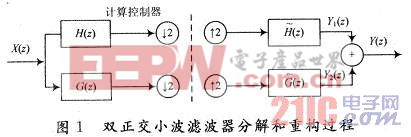

- 現代計算機和通信系統中廣泛采用數字信號處理的技術和方法,其基本思路是先把信號用一系列的數字來表示,然后對這些數字信號進行各種快速的數學運算。其目的是多種多樣的,有的是為了加密,有的是為了去掉噪聲等無

- 關鍵字:

設計 濾波器 HDL Verilog 基于

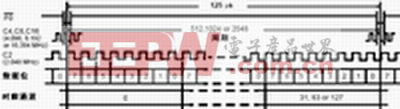

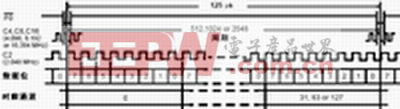

- ST-BUS總線接口模塊的Verilog HDL設計,ST-BUS是廣泛應用于E1通信設備內部的一種模塊間通信總線。結合某專用通信系統E1接口轉換板的設計,本文對ST-BUS總線進行了介紹,討論了ST-BUS總線接口收發模塊的設計方法,給出了Verilog HDL實現和模塊的時序仿真圖。

- 關鍵字:

HDL 設計 Verilog 模塊 總線 接口 ST-BUS

- PLD/FPGA硬件語言設計verilog HDL,HDL概述 隨著EDA技術的發展,使用硬件語言設計PLD/FPGA成為一種趨勢。目前最主要的硬件描述語言是VHDL和verilog HDL及System Verilog。 VHDL發展的較早,語法嚴格;而Verilog HDL是在C語言的基礎上發展起來的一種硬

- 關鍵字:

verilog HDL 設計 語言 硬件 PLD/FPGA

- Verilog HDL與VHDL及FPGA的比較分析, Verilog HDL 優點:類似C語言,上手容易,靈活。大小寫敏感。在寫激勵和建模方面有優勢。 缺點:很多錯誤在編譯的時候不能被發現。 VHDL 優點:語法嚴謹,層次結構清晰。 缺點:熟悉時間長,不夠靈

- 關鍵字:

比較 分析 FPGA VHDL HDL Verilog

- 摘要:通用異步收發器UART常用于微機和外設之間的數據交換,針對UART的特點,提出了一種基于Ver4log HDL的UART設計方法。采用自頂向下的設計路線,結合狀態機的描述形式,使用硬件描述語言設計UART的頂層模塊及各個子

- 關鍵字:

Verilog UART HDL 模塊設計

- 基于FPGA和DDS的信號源設計,1 引言

直接數字頻率合成DDS(Direct Digital Synthesizer)是基于奈奎斯特抽樣定理理論和現代器件生產技術發展的一種新的頻率合成技術。與第二代基于鎖相環頻率合成技術相比,DDS具有頻率切換時間短、頻率分辨率

- 關鍵字:

設計 信號源 DDS FPGA 基于 FPGA,DDS,Verilog HDL

- Altium繼續在其下一代電子產品設計軟件Altium Designer中提供新功能,幫助電子產品設計人員站在新科技和潮流的最前沿。

Altium公司首席執行官Nick Martin表示:“我們認為,讓用戶等待每隔數年才更新一次版本的產業模型已經完全不符合當前的需求。”

此次最重要的新特性是基于網絡的軟件許可證管理和訪問選項。它使電子產品設計人員能夠有效地管理設計團隊、工作量及項目。

Altium Designer中的其他新特性包括針對板卡級設計人員的定制FP

- 關鍵字:

Altium 電子產品設計 FPGA HDL

- 直接數字頻率合成技術(Direct Digital Synthesize,DDS)是繼直接頻率合成技術和鎖相式頻率合成技術之后的第三代頻率合成技術。它采用全數字技術,并從相位角度出發進行頻率合成。隨著微電子技術和數字集成電路的飛速

- 關鍵字:

Verilog HDL DDS 仿真

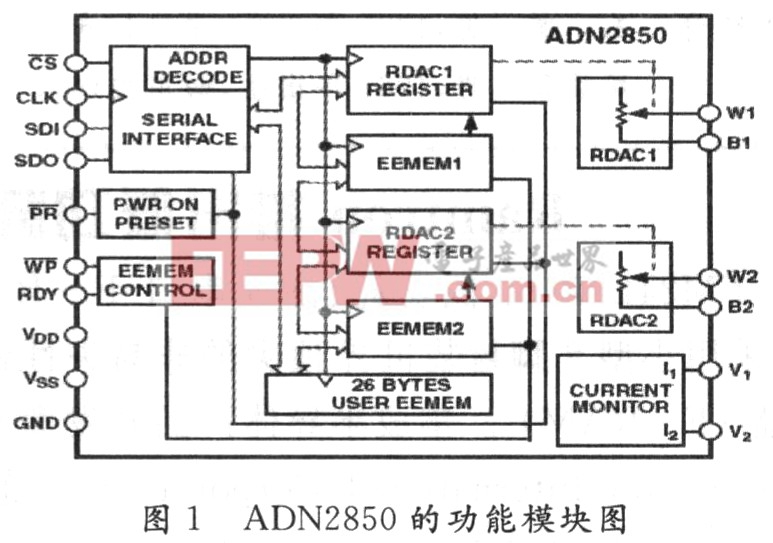

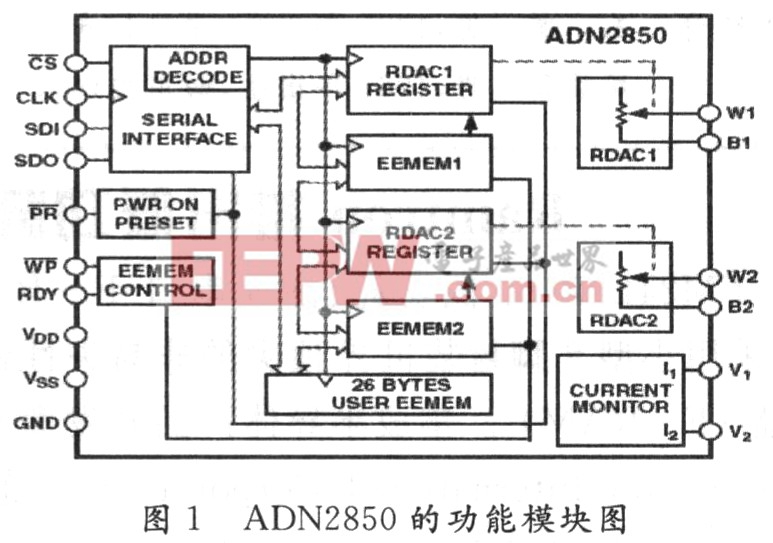

- 摘要:數字電位器由于可調精度高,更穩定,定位更準確,操作更方便,數據可長期保存和隨時刷新等優點,在某些場合具有模擬電位器不可比擬的優勢。論述對數字電位器ADN2850的一種方便的控制方法,通過計算機上的串口直

- 關鍵字:

串口 控制 ADN2850 數字電位器 Verilog HDL 基于

- 針對機器人伺服控制系統高速度、高精度的要求,介紹一種全數字化的基于神經網絡控制的直流電機速度伺服控制系統的設計方案。速度控制器采用BP網絡參數辨識自適應控制,并將其在FPGA進行硬件實現;同時用Nios II軟核處理器作為上位機,構成一個完整的速度伺服控制器的片上可編程系統(SOPC)。實驗結果表明,該控制系統具有較高的控制精度、較好的穩定性和靈活性。

- 關鍵字:

SOPC 系統 控制器 速度 神經網絡 電機 基于 神經網絡 伺服控制 現場可編程門陣列 Verilog HDL

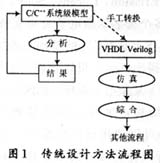

- 隨著集成電路制造技術的迅速發展,SOC設計已經成為當今集成電路設計的發展方向。SO C設計的復雜性對集成電路設計的各個層次,特別是對系統級芯片設計層次,帶來了新挑戰,原有的HDL難以滿足新的設計要求。

硬件設計領域有2種主要的設計語言:VHDL和Verilog HDL。而兩種語言的標準不統一,導致軟硬件設計工程師之間工作交流出現障礙,工作效率較低。因此,集成電路設計界一直在尋找一種能同時實現較高層次的軟件和硬件描述的系統級設計語言。Synopsys公司與Coware公司針對各方對系統級設計語言的

- 關鍵字:

SOC SystemC 集成電路 VHDL Verilog HDL

x-hdl介紹

您好,目前還沒有人創建詞條x-hdl!

歡迎您創建該詞條,闡述對x-hdl的理解,并與今后在此搜索x-hdl的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473