- 實驗目的(1)熟悉和掌握FPGA開發流程和Lattice Diamond軟件使用方法;(2)通過實驗理解和掌握分頻器原理;(3)學習用Verilog HDL行為級描述時序邏輯電路。實驗任務設計一個任意整數分頻器。實驗原理時鐘信號的處理是FPGA的特色之一,因此分頻器也是FPGA設計中使用頻率非常高的基本設計之一。一般在FPGA中都有集成的鎖相環可以實現各種時鐘的分頻和倍頻設計,但是通過語言設計進行時鐘分頻是最基本的訓練,在對時鐘要求不高的設計時也能節省鎖相環資源。在本實驗中我們將實現任意整數的分頻器,分頻

- 關鍵字:

分頻器 FPGA Lattice Diamond Verilog HDL

- 實驗目的(1)熟悉和掌握FPGA開發流程和Lattice Diamond軟件使用方法;(2)通過實驗理解和掌握扭環形計數器原理;(3)學習用Verilog HDL行為級描述時序邏輯電路。實驗任務設計一個右移扭環形計數器。實驗原理將移位寄存器的輸出非q0連接到觸發器q3的輸入,這樣就構成了一個扭環形計數器。初始化復位時,給q0一個初值0000,則在循環過程中依次為:000010001100111011110111001100010000。Verilog HDL建模描述用行為級描述右移扭環形計數器程序清單tw

- 關鍵字:

扭環形計數器 FPGA Lattice Diamond Verilog HDL

- 實驗目的(1)熟悉和掌握FPGA開發流程和Lattice Diamond軟件使用方法;(2)通過實驗理解和掌握環形計數器原理;(3)學習用Verilog HDL行為級描述時序邏輯電路。實驗任務設計一個4位右循環一個1的環形計數器。實驗原理將移位寄存器的輸出q0連接到觸發器q3的輸入,并且在這4個觸發器中只有一個輸出為1,另外3個為0,這樣就構成了一個環形計數器。初始化復位時,給q0一個置位信號,則唯一的1將在環形計數器中循環移位,每4個時鐘同期輸出一個高電平脈沖。Verilog HDL建模描述用行為級描述

- 關鍵字:

環形計數器 FPGA Lattice Diamond Verilog HDL

- 實驗目的(1)熟悉和掌握FPGA開發流程和Lattice Diamond軟件使用方法;(2)通過實驗理解和掌握移位寄存器原理;(3)學習用Verilog HDL行為級描述時序邏輯電路。實驗任務本實驗的任務是設計一個7位右移并行輸入、串行輸出的移位寄存器。實驗原理如果將多個觸發器級聯就構成一個多位的移位寄存器,如下圖所示,是以4位移位寄存器為例的邏輯電路圖,其中的LD/SHIFT是一個置數/移位控制信號。當LD/SHIFT為1時,在CP作用下,從輸入端A、B、C、D并行接收數據;當LD/SHIFT為0時,在

- 關鍵字:

移位寄存器 FPGA Lattice Diamond Verilog HDL

- 實驗目的(1)熟悉和掌握FPGA開發流程和Lattice Diamond軟件使用方法;(2)通過實驗理解和掌握JK觸發器原理;(3)學習用Verilog HDL語言行為機描述方法描述JK觸發器電路。實驗任務本實驗的任務是設計一個JK觸發器實驗原理帶使能端RS鎖存器的輸入端R=S=1時,鎖存器的次態不確定,這一因素限制了其應用。為了解決這個問題,根據雙穩態元件兩個輸出端互補的特點,用Q和非Q反饋控制輸入信號,并用J代替S,用K代替R,構成了J-K鎖存器。Verilog HDL建模描述用行為級描述實現的帶異步

- 關鍵字:

JK觸發器 FPGA Lattice Diamond Verilog HDL

- 實驗目的(1)熟悉和掌握FPGA開發流程和Lattice Diamond軟件使用方法;(2)通過實驗理解和掌握D觸發器原理;(3)學習用Verilog HDL語言行為機描述方法描述D觸發器電路。實驗任務本實驗的任務是描述一個帶有邊沿觸發的同步D觸發器電路,并通過STEP FPGA開發板的12MHz晶振作為觸發器時鐘信號clk,撥碼開關的狀態作為觸發器輸入信號d,觸發器的輸出信號q和~q,用來分別驅動開發板上的LED,在clk上升沿的驅動下,當撥碼開關狀態變化時LED狀態發生相應變化。實驗原理從D觸發器的特

- 關鍵字:

D觸發器 FPGA Lattice Diamond Verilog HDL

- 實驗目的(1)熟悉和掌握FPGA開發流程和Lattice Diamond軟件使用方法;(2)通過實驗理解和掌握RS觸發器原理;(3)學習用Verilog HDL語言行為級描述方法描述RS觸發器電路。實驗任務本實驗的任務是描述一個RS觸發器電路,并通過STEP FPGA開發板的12MHz晶振作為觸發器時鐘信號clk,撥碼開關的狀態作為觸發器輸入信號S,R,觸發器的輸出信號Q和非Q,用來分別驅動開發板上的LED,在clk上升沿的驅動下,當撥碼開關狀態變化時LED狀態發生相應變化。實驗原理基本RS觸發器可以由兩

- 關鍵字:

RS觸發器 FPGA Lattice Diamond Verilog HDL

- 1. 實驗目的(1)熟悉和掌握FPGA開發流程和Lattice Diamond軟件使用方法;(2)通過實驗理解和掌握數碼管驅動;(3)學習用Verilog HDL描述數碼管驅動電路。2. 實驗任務在數碼管上顯示數字。3. 實驗原理數碼管是工程設計中使用很廣的一種顯示輸出器件。一個7段數碼管(如果包括右下的小點可以認為是8段)分別由a、b、c、d、e、f、g位段和表示小數點的dp位段組成。實際是由8個LED燈組成的,控制每個LED的點亮或熄滅實現數字顯示。通常數碼管分為共陽極數碼管和共陰極數碼管,結構如下圖

- 關鍵字:

七段數碼管 FPGA Lattice Diamond Verilog HDL

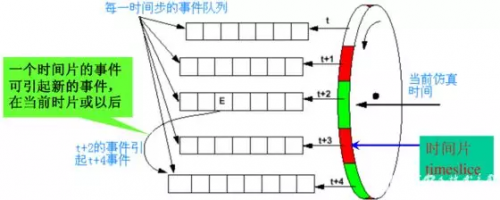

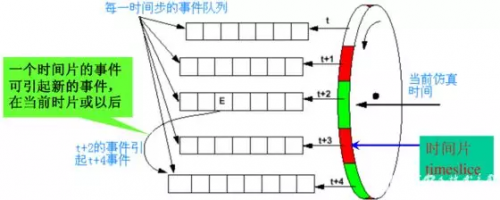

- 目前,HDL仿真器主要有三種實現算法(機制):基于時間的算法(Time-Based)、基于事件的算法(Event-Based,EBS)和基于周期的算法(Cycle-Based,CBS) 基于時間的算法適合處理連續的時間及變量,其會在每一個時間點對所有的電路元件進行計算。但是,在大部分情況下,每一個時間點只有約2%~10%的電路處于活動(運行)狀態,所以該算法效率非常低。 基于事件的算法適合處理離散的時間、狀態和變量。該算法只有在電路狀態發生變化時才進行處理,只仿真那些可能引起電路狀態改變的元件。仿

- 關鍵字:

HDL 仿真器

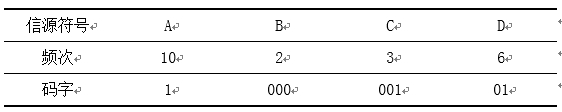

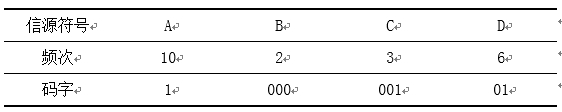

- Huffman編碼是一種可變字長的無損壓縮編碼。根據字符出現的概率得到的可變字長編碼表是Huffman編碼的核心。概率低的字符使用較短的編碼,概率高的字符使用的長的編碼。 Huffman編碼的具體方法是將序列中的信源符號先按出現的頻次排序,把兩個最小的頻次相加,作為新的頻次和剩余的頻次重新排序,再把最小的兩個頻次相加,再重新排序,直到最后變成序列的總長度。每次挑出的最小兩個頻次所對應的信源符號或信源符號集構成二叉樹的左右兩支,對這左右兩支賦予“0”和“1”的權重。符號的編碼從樹的根部開始一直到達符號

- 關鍵字:

哈夫曼編碼 HDL

- 智能家居多媒體聲光電同步演示系統方案-HDL建筑智能照明控制系統借助各種不同的“預設置”控制方式和控制元件,對不同時間不同環境的光照度進行精確設置和合理管理。

- 關鍵字:

HDL 智能家居

- 新手福音:概述學習FPGA的一些常見誤區-很多剛開始學習FPGA的朋友們經常會遇上一些誤區而無從解決,FPGA為什么是可以編程的?通過HDL語言怎么看都看不出硬件結構?...本文就這個方面進行解析。

- 關鍵字:

可編程邏輯器件 FPGA HDL FPGA教程

- 把HDL模塊用NGC格式加密并在其他項目中調用-前面創新網網友Ricky Su發了篇博文《 說說FPGA中的黑盒子(BlackBox)》,學習了感覺很好用,最近在網上又找到一篇講該方面內容的文章,感覺寫的很好轉發來與大家共享,文章如下

- 關鍵字:

NGC HDL

- Verilog HDL簡明教程(2)-模塊是Verilog 的基本描述單位,用于描述某個設計的功能或結構及其與其他模塊通信的外部端口。

- 關鍵字:

Verilog HDL

- Verilog HDL 不僅提供描述設計的能力,而且提供對激勵、控制、存儲響應和設計驗證的建模能力。激勵和控制可用初始化語句產生。驗證運行過程中的響應可以作為 “ 變化時保存 ” 或作為選通的數據存儲。最后,設計驗證可以通過在初始化語句中寫入相應的語句自動與期望的響應值比較完成。

- 關鍵字:

Verilog HDL 設計模擬

x-hdl介紹

您好,目前還沒有人創建詞條x-hdl!

歡迎您創建該詞條,闡述對x-hdl的理解,并與今后在此搜索x-hdl的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473