介紹了HDLC協議控制器的IP核方案及實現方法,分別對發送和接收模塊進行了分析,給出了仿真波形圖。該設計采用Verilog HDL語言進行描述,用ModelSim SE 6.0進行了功能仿真。

關鍵字:

IP核 Verilog HDLC協議控制器

Verilog HDL是硬件描述語言的一種,用于數字電子系統設計。它允許設計者用它來進行各種級別的邏輯設計,可以用它進行數字邏輯系統的仿真驗證、時序分析、邏輯綜合。它是目前應用最廣泛的一種硬件描述語言之一。Verilog HDL是在1983年由GDA公司的Phil Moorby首創的。

關鍵字:

VerilogHDL VHDL Verilog-XL 華清遠見

本節通過Verilog HDL語言編寫一個具有“百分秒、秒、分”計時功能的數字跑表,可以實現一個小時以內精確至百分之一秒的計時。

關鍵字:

計數器 數字跑表 Verilog

文章簡要介紹了從光電容積脈搏波中提取出的特征值有助于在醫學領域中分析人體的病理特征。為了檢測脈搏波的血流參數,整個系統采用Altera公司cyclone系列的FPGA開發平臺,運用硬件語言Verilog HDL編程設計了波形參數的檢測模塊,通過設計IP核進行數據處理并實現了脈搏波的實時檢測。使用了QuartusⅡ、Icarus verilog和GTKwave軟件進行綜合仿真,并通過FPGA原型驗證。創新點在于采用FPGA通過硬件的方式提高了實時檢測的速度,降低了開發成本,增強了可攜帶性。

關鍵字:

病理特征 Verilog 原型驗證

簡述了I2C總線的特點;介紹了開發FPGA時I2C總線模塊的設計思路;給出并解釋了用Verilog HDL實現部分I2C總線功能的程序,以及I2C總線主從模式下的仿真時序圖。

關鍵字:

Verilog I2C 仿真時序

SMBus是一種高效的同步串行總線。通過分析SMBus總線協議,提出了一種運行于基于PCI-Express技術的橋接芯片上的SMBus控制器的設計方案,并且用Verilog語言描述,最后在Altera公司的FPGA上得以實現。通過仿真測試,證明該方法是穩定有效的。

關鍵字:

SMBus總線 Verilog 有限狀態機

LCD顯示屏的應用越來越廣,數量越來越多。LCD顯示屏應用廣泛,無處不在。如家庭各種電器設備。更常見是用于各種公共場合如體育館、廣場等商業用途。給我們傳遞一種更為直觀、生動的信息。從此我們的生活發生了巨大改變。巨大的應用巨大的市場帶來了巨大的商機。基于FPGA的LCD顯示的3D影像是為了LCD顯示屏的信息量更多,滿足人需求。

關鍵字:

IP核 3D圖像處理器 FPGA LCD Verilog

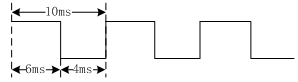

一、 功能描述 脈沖寬度調制(pulse width modelation)簡稱PWM,利用微處理器的數字輸出來對模擬電路進行控制的一種非常有效的技術,廣泛應用在從測量、通信到功率控制與變換的許多領域中脈沖寬度調制是利用微處理器的數字輸出來對模擬電路進行控制的一種非常有效的技術,廣泛應用在從測量、通信到功率控制與變換的許多領域中。 在本章的應用中可以認為PWM就是一種方波。如圖所示:

PWM波形圖 上圖是一個周期為10ms,高電平為

關鍵字:

PWM verilog

由于Verilog HDL和 VHDL 行為描述用于綜合的歷史還只有短短的幾年,可綜合風格的Verilog HDL 和VHDL的語法只是它們各自語言的一個子集。又由于HDL的可綜合性研究近年來非常活躍,可綜合子集的國際標準目前尚未最后形

關鍵字:

Verilog HDL 進階 代碼

task和function說明語句的區別task和function說明語句分別用來定義任務和函數。利用任務和函數可以把一個很大的程序模塊分解成許多較小的任務和函數便于理解和調試。輸入、輸出和總線信號的值可以傳入或傳出任務和函

關鍵字:

function Verilog task HDL

上周我跟我同事說,“ 兩種語言阻礙了嵌入式系統開發人員和軟件工程師借助Zynq SOCs來提升系統性能。”那就是“Verilog” 和 “VHDL”正如期待那樣,這已經得到了解決—因為SD

關鍵字:

Verilog VHDL SDSoC

高速長線陣CCD(電荷耦合器)具有低功耗,小體積,高精度等優勢,廣泛應用于航天退掃系統中的圖像數據采集。而CCD驅動電路設計是CCD正常工作的關鍵問題之一,CCD驅動信號時序是一組相位要求嚴格的脈沖信號,只有時序信

關鍵字:

CCD 線陣 FPGA verilog HDL

摘要:空間矢量脈寬調制算法是電壓型逆變器控制方面的研究熱點,廣泛應用于三相電力系統中。基于硬件的FPGA/CPLD芯片能滿足該算法對處理速度、實時性、可靠性較高的要求,本文利用Verilog HDL實現空間矢量脈寬調制算

關鍵字:

同步電動機 電壓型逆變器 Verilog HDL

為了得到比傳統片上網絡的網絡資源接口(NI)更高的數據傳輸效率和更加穩定的數據傳輸效果,提出了一種新的高效網絡接口的設計方法,并采用Verilog HDL語言對相關模塊進行編程,實現了高效傳輸功能,同時又滿足核內路由的設計要求。最終通過仿真軟件Xilinx ISE Design Suite 12.3和ModelSim SE 6.2b得到了滿足設計要求的仿真結果。

關鍵字:

片上網絡 網絡資源接口 核內路由 Verilog HDL

verilog-a介紹

您好,目前還沒有人創建詞條verilog-a!

歡迎您創建該詞條,闡述對verilog-a的理解,并與今后在此搜索verilog-a的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473