fpga 文章 進入fpga技術社區

實驗15:環形計數器

- 實驗目的(1)熟悉和掌握FPGA開發流程和Lattice Diamond軟件使用方法;(2)通過實驗理解和掌握環形計數器原理;(3)學習用Verilog HDL行為級描述時序邏輯電路。實驗任務設計一個4位右循環一個1的環形計數器。實驗原理將移位寄存器的輸出q0連接到觸發器q3的輸入,并且在這4個觸發器中只有一個輸出為1,另外3個為0,這樣就構成了一個環形計數器。初始化復位時,給q0一個置位信號,則唯一的1將在環形計數器中循環移位,每4個時鐘同期輸出一個高電平脈沖。Verilog HDL建模描述用行為級描述

- 關鍵字: 環形計數器 FPGA Lattice Diamond Verilog HDL

實驗14:移位寄存器

- 實驗目的(1)熟悉和掌握FPGA開發流程和Lattice Diamond軟件使用方法;(2)通過實驗理解和掌握移位寄存器原理;(3)學習用Verilog HDL行為級描述時序邏輯電路。實驗任務本實驗的任務是設計一個7位右移并行輸入、串行輸出的移位寄存器。實驗原理如果將多個觸發器級聯就構成一個多位的移位寄存器,如下圖所示,是以4位移位寄存器為例的邏輯電路圖,其中的LD/SHIFT是一個置數/移位控制信號。當LD/SHIFT為1時,在CP作用下,從輸入端A、B、C、D并行接收數據;當LD/SHIFT為0時,在

- 關鍵字: 移位寄存器 FPGA Lattice Diamond Verilog HDL

實驗13:JK觸發器

- 實驗目的(1)熟悉和掌握FPGA開發流程和Lattice Diamond軟件使用方法;(2)通過實驗理解和掌握JK觸發器原理;(3)學習用Verilog HDL語言行為機描述方法描述JK觸發器電路。實驗任務本實驗的任務是設計一個JK觸發器實驗原理帶使能端RS鎖存器的輸入端R=S=1時,鎖存器的次態不確定,這一因素限制了其應用。為了解決這個問題,根據雙穩態元件兩個輸出端互補的特點,用Q和非Q反饋控制輸入信號,并用J代替S,用K代替R,構成了J-K鎖存器。Verilog HDL建模描述用行為級描述實現的帶異步

- 關鍵字: JK觸發器 FPGA Lattice Diamond Verilog HDL

實驗12:邊沿觸發的D觸發器

- 實驗目的(1)熟悉和掌握FPGA開發流程和Lattice Diamond軟件使用方法;(2)通過實驗理解和掌握D觸發器原理;(3)學習用Verilog HDL語言行為機描述方法描述D觸發器電路。實驗任務本實驗的任務是描述一個帶有邊沿觸發的同步D觸發器電路,并通過STEP FPGA開發板的12MHz晶振作為觸發器時鐘信號clk,撥碼開關的狀態作為觸發器輸入信號d,觸發器的輸出信號q和~q,用來分別驅動開發板上的LED,在clk上升沿的驅動下,當撥碼開關狀態變化時LED狀態發生相應變化。實驗原理從D觸發器的特

- 關鍵字: D觸發器 FPGA Lattice Diamond Verilog HDL

實驗11:RS觸發器

- 實驗目的(1)熟悉和掌握FPGA開發流程和Lattice Diamond軟件使用方法;(2)通過實驗理解和掌握RS觸發器原理;(3)學習用Verilog HDL語言行為級描述方法描述RS觸發器電路。實驗任務本實驗的任務是描述一個RS觸發器電路,并通過STEP FPGA開發板的12MHz晶振作為觸發器時鐘信號clk,撥碼開關的狀態作為觸發器輸入信號S,R,觸發器的輸出信號Q和非Q,用來分別驅動開發板上的LED,在clk上升沿的驅動下,當撥碼開關狀態變化時LED狀態發生相應變化。實驗原理基本RS觸發器可以由兩

- 關鍵字: RS觸發器 FPGA Lattice Diamond Verilog HDL

實驗10:七段數碼管

- 1. 實驗目的(1)熟悉和掌握FPGA開發流程和Lattice Diamond軟件使用方法;(2)通過實驗理解和掌握數碼管驅動;(3)學習用Verilog HDL描述數碼管驅動電路。2. 實驗任務在數碼管上顯示數字。3. 實驗原理數碼管是工程設計中使用很廣的一種顯示輸出器件。一個7段數碼管(如果包括右下的小點可以認為是8段)分別由a、b、c、d、e、f、g位段和表示小數點的dp位段組成。實際是由8個LED燈組成的,控制每個LED的點亮或熄滅實現數字顯示。通常數碼管分為共陽極數碼管和共陰極數碼管,結構如下圖

- 關鍵字: 七段數碼管 FPGA Lattice Diamond Verilog HDL

Microchip PolarFire FPGA單芯片加密設計流程 成功通過英國國家網絡安全中心審查

- 安全當前已成為各垂直市場所有設計的當務之急。今天,有進一步證據向系統架構師和設計人員證明,使用Microchip Technology Inc.(美國微芯科技公司)的PolarFire FPGA 可有力保障通信、工業、航空航天、國防、核及其他系統的安全性。英國政府的國家網絡安全中心(NCSC)根據嚴格的器件級彈性要求,對采用單芯片加密設計流程的PolarFire FPGA器件進行了審查。Microchip FPGA 業務部技術研究員 Tim Morin 表示:“NCSC進行了非常嚴格的分析和審查。Micr

- 關鍵字: Microchip PolarFire FPGA 加密設計 英國國家網絡安全中心

fpga介紹

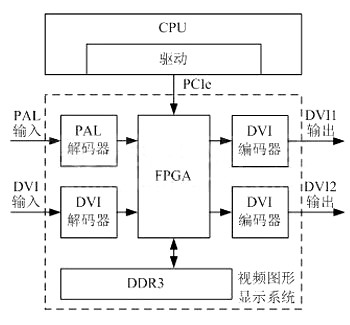

FPGA是英文Field-Programmable Gate Array的縮寫,即現場可編程門陣列,它是在PAL、GAL、EPLD等可編程器件的基礎上進一步發展的產物。它是作為專用集成電路(ASIC)領域中的一種半定制電路而出現的,既解決了定制電路的不足,又克服了原有可編程器件門電路數有限的缺點。

FPGA采用了邏輯單元陣列LCA(Logic Cell Array)這樣一個新概念,內部包括可 [ 查看詳細 ]