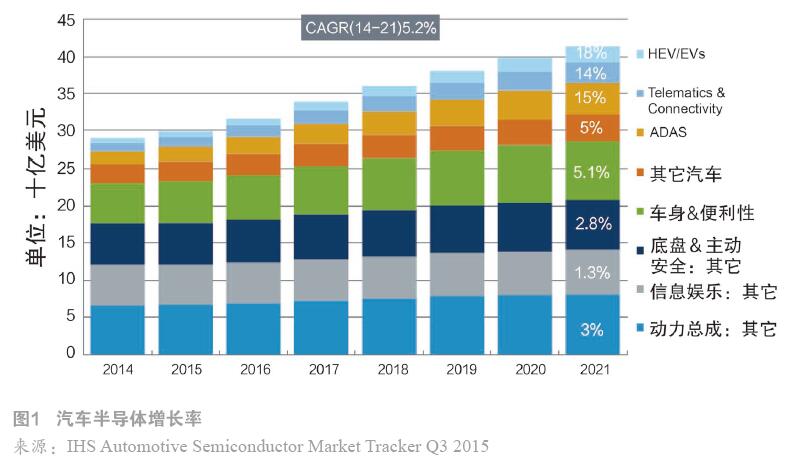

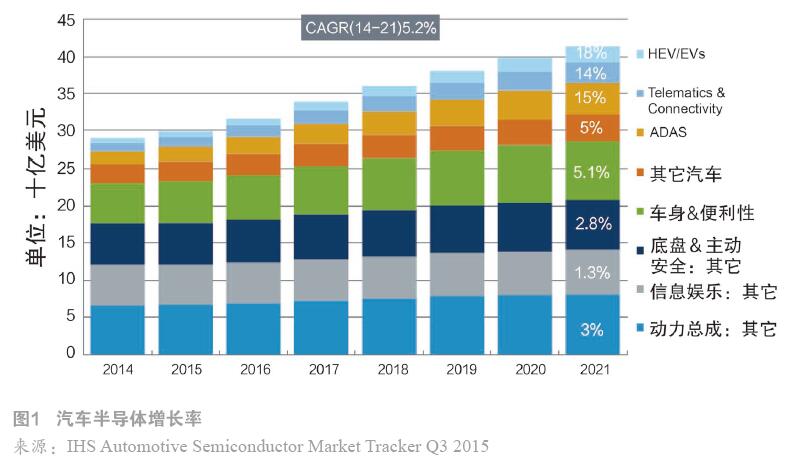

- 在“2017慕尼黑上海電子展”前夕的“汽車技術日”上,ISSI技術市場經理田步嚴介紹了車用存儲器市場,包括:信息娛樂、ADAS、儀表總成、connectivity telematics四大類。

- 關鍵字:

汽車 SRAM DRAM SDRAM e.MMC 201704

- 實驗目的:改變“點燈大法”的執行地點,從NandFlash的Steppingstone轉到SDRAM中執行,借此掌握存儲控制器的使用。 實 驗環境及說明:恒頤S3C2410開發板H2410。H2410核心板擴展有64MB的SDRAM,用于設置程序堆棧和存放各種變量。SDRAM選用了兩 片三星公司的K4S561632(4M*16bit*4BANK),兩片拼成32位數據寬度的SDRAM存儲系統,并映射到S3C2410的 SROM/SDRAM的BANK6,地址范圍是0x300

- 關鍵字:

ARM SDRAM

- 存儲器共有13個寄存器,BANK0~BANK5只需要設置BWSCON和BANKCONx(x為0~5)兩個寄存器;BANK6、BANK7外接SDRAM時,除了BWSCON和BANKCONx(x為6、7)外,還要設置REFRESH、BANKSIZE、MRSRB6、MRSRB7等4個寄存器。下面分類說明(“[y:x]”表示占據了寄存器的位x、x+1、……、y):

1. 位寬和等待控制寄存器BWSCON(Bus Width & Wait Sta

- 關鍵字:

ARM SDRAM

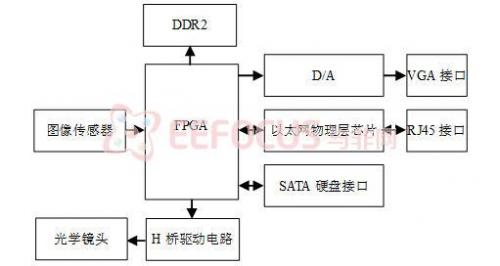

- 摘要:為了解決在一個屏幕上收看多個信號源的問題,對基于FPGA技術的視頻圖像畫面分割器進行了研究。研究的主要特色在于構建了以FPGA為核心器件的視頻畫面分割的硬件平臺,首先,將DVI視頻信號,經視頻解碼芯片轉換為

- 關鍵字:

FPGA DDR2 SDRAM 視頻提取 圖像合成

- 高速SDRAM存儲器接口電路設計SDRAM可作為軟嵌入式系統的(NIOS II)的程序運行空間,或者作為大量數據的緩沖區。SDRAM是通用的存儲設備,只要容量和數據位寬相同,不同公司生產的芯片都是兼容的。一般比較常用的SDRAM

- 關鍵字:

SDRAM FPGA 最小系統 電路分析

- 實現數據的高速大容量存儲是數據采集系統中的一項關鍵技術。本設計采用Altera 公司Cyclone系列的FPGA 完成了對DDR SDRAM 的控制,以狀態機來描述對DDR SDRAM 的各種時序操作,設計了DDR SDRAM 的數據與命令接口。用控

- 關鍵字:

SDRAM FPGA DDR 控制器

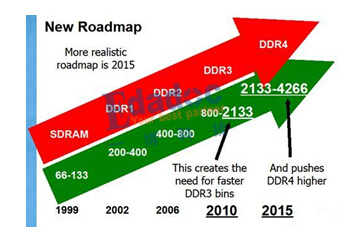

- DDR3 SDRAM內存的總線速率達到600 Mbps to 1.6 Gbps (300 to 800 MHz),1.5V的低功耗工作電壓,采用90nm制程達到2Gbits的高密度。這個架構毫無疑問更快、更大,每比特的功耗也更低,但是如何實現FPGA和DDR3 SDRAM DI

- 關鍵字:

SDRAM FPGA DDR3 接口設計

- 今天我們來講的是SDRAM的架構以及設計,這也是小墨第一次接觸架構,也談不上給大家講,就是把我理解的當做一個筆記分享給大家,我也試著做了一個SDRAM 的架構word文檔,在文章的后面,喜歡的朋友可以下載下來看一下

- 關鍵字:

SDRAM FPGA

- 高速電路設計領域,關于布線有一種幾乎是公理的認識,即“等長”走線,認為走線只要等長就一定滿足時序需求,就不會存在時序問題。本文對常用高速器件的互連時序建立模型,并給出一般性的時序分析公式。為

- 關鍵字:

PCB DDR SDRAM PHY芯片

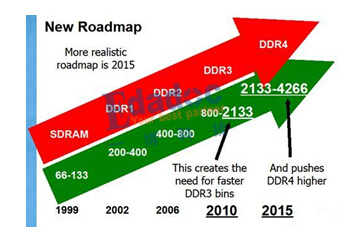

- DRAM (動態隨機訪問存儲器)對設計人員特別具有吸引力,因為它提供了廣泛的性能,用于各種計算機和嵌入式系統的存儲系統設計中。本文概括闡述了DRAM 的概念,及介紹了SDRAM、DDR SDRAM、DDR2 SDRAM、DDR3 SDRAM、DD

- 關鍵字:

存儲器 DRAM SDRAM

- SDRAM與DDR SDRAM

SDRAM是比較久遠的事情了,但我們一說到它肯定不會和 DDR混淆,我們通常理解的SDRAM其實是SDR SDRAM,為SDRAM的第一代,而DDR1則為第二代,乃至到我們現在使用的DDR4,其實為第五代SDRAM,在此需要澄清一下。以示區別,后續文 章里面用SDR來特指SDR SDRAM,而DDR就特指DDR SDRAM了。

就像很多人回復的一樣,他們的本質區別就是周期操作方 式(也稱時鐘采樣)的差異,這就導致后面設計上很大的不同。SDR都是“

- 關鍵字:

DDR SDRAM

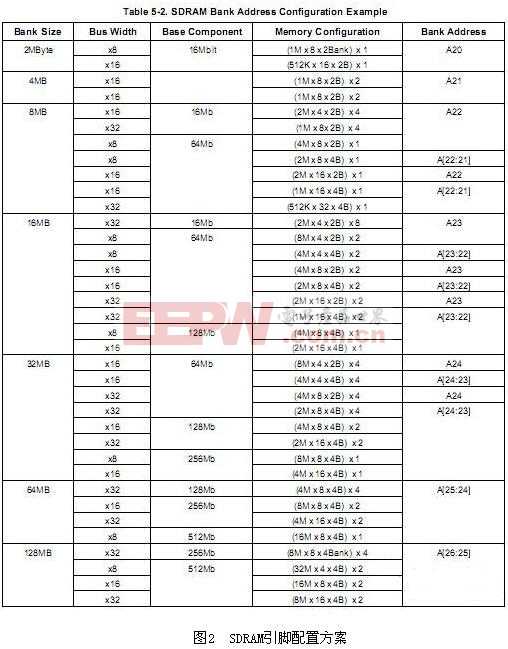

- 介紹SDRAM電路設計之前先了解下SDRAM的尋址原理。SDRAM內部是一個存儲陣列,可以把它想象成一個表格,和表格的檢索原理一樣,先指定行,再指定列,

- 關鍵字:

SDRAM 電路設計

- RAMRAM是指通過指令可以隨機的、個別的對各個存儲單元進行訪問的存儲器,一般訪問時間基本固定,而與存儲單元地址無關。RAM的速度比較快,但其保

- 關鍵字:

SRAM DRAM SDRAM 比較

- 基于Xilinx V5的DDR2數據解析功能實現,摘要:介紹了一種基于Xilinx V5芯片的硬件板卡上,利用Verilog硬件編程語言,來實現DDR2對數據文件解析的目的:分析了CPCI總線與FPGA之間的通信特點;然后根據收到的數據文件要求,介紹了DDR2的使用方法;最后介紹了對

- 關鍵字:

Xilinx Verilog DDR2 數據解析 信號波形

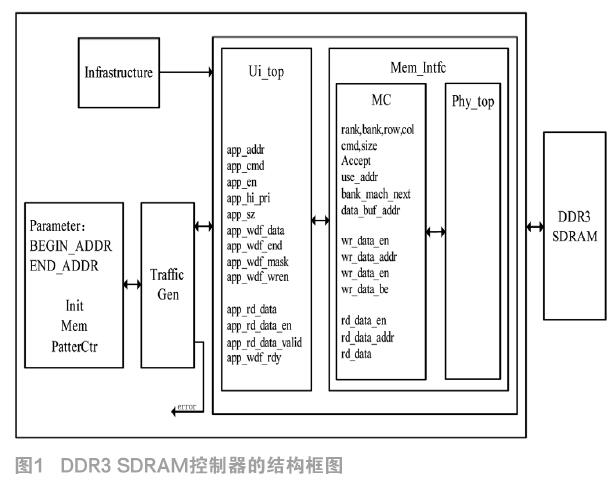

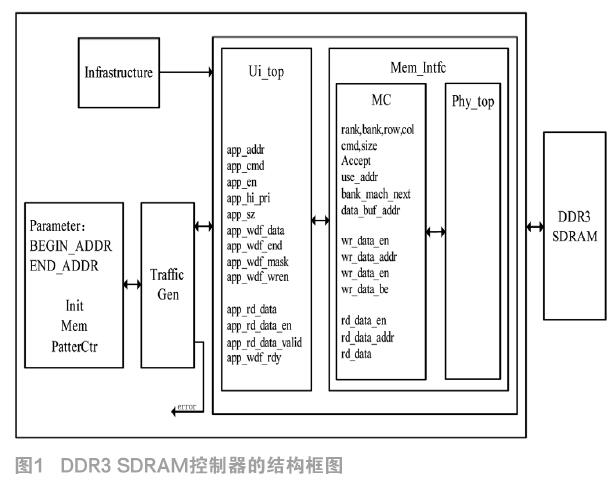

- 為了使DDR3 SDRAM更方便、多樣地用于工程開發中,本文對XILINX公司DDR3 SDRAM提供的MIG核進行了分析研究,并在此基礎上實現了大容量數據緩沖區的邏輯設計。通過對系統中各模塊的作用及相互間關系的研究,發現該控制器256位接口對工程開發十分不便,通過創建FIFO控制系統和讀寫接口FIFO的方式,將接口轉換為64位。該方案對控制核重新構建并上板測試,均符合高速數據傳輸緩存的要求,使DDR3成為一個大容量且可控的高速FIFO。

- 關鍵字:

MIG核 FIFO DDR3 SDRAM 201608

ddr2-sdram介紹

您好,目前還沒有人創建詞條ddr2-sdram!

歡迎您創建該詞條,闡述對ddr2-sdram的理解,并與今后在此搜索ddr2-sdram的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473