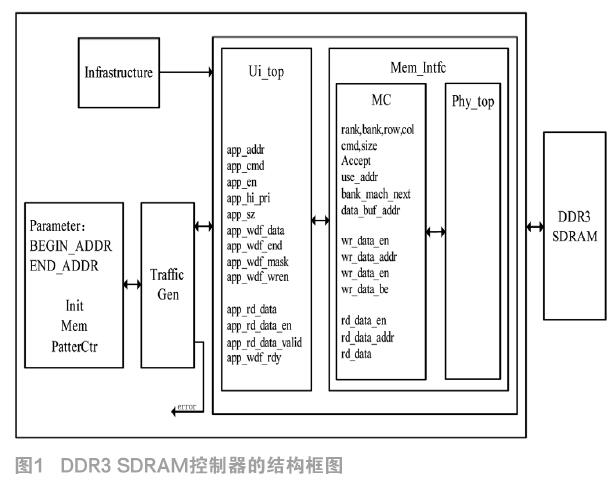

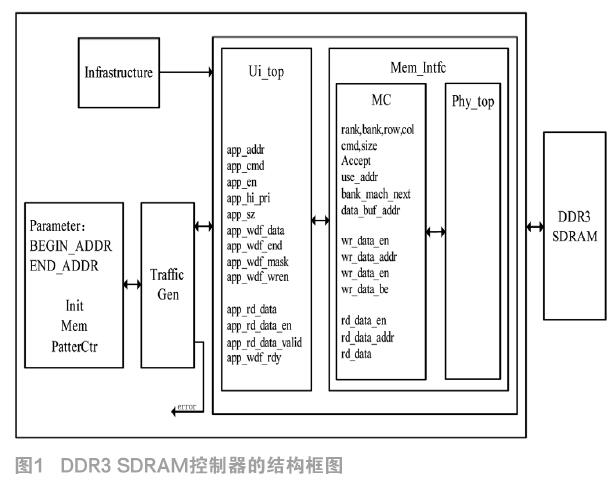

- 為了使DDR3 SDRAM更方便、多樣地用于工程開發中,本文對XILINX公司DDR3 SDRAM提供的MIG核進行了分析研究,并在此基礎上實現了大容量數據緩沖區的邏輯設計。通過對系統中各模塊的作用及相互間關系的研究,發現該控制器256位接口對工程開發十分不便,通過創建FIFO控制系統和讀寫接口FIFO的方式,將接口轉換為64位。該方案對控制核重新構建并上板測試,均符合高速數據傳輸緩存的要求,使DDR3成為一個大容量且可控的高速FIFO。

- 關鍵字:

MIG核 FIFO DDR3 SDRAM 201608

mig核介紹

您好,目前還沒有人創建詞條mig核!

歡迎您創建該詞條,闡述對mig核的理解,并與今后在此搜索mig核的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473