摘要:為降低設計成本,縮短設計周期,提出一種基于VHDL的洗衣機控制器的設計方案。該方案采用模塊化的設計思想,并使用狀態機完成控制模塊的設計。整個系統在QuartusⅡ開發平臺上完成設計、編譯和仿真,并在FPGA硬件

關鍵字:

洗衣機控制器 狀態機 FPGA VHDL QuartusⅡ

摘要:采用FPGA進行的數字電路設計具有更大的靈活性和通用性,已成為目前數字電路設計的主流方法之一。本文給出一種基于FPGA的數字鐘設計方案。該方案采用VHDL設計底層模塊,采用電路原理圖設計頂層系統。整個系統在

關鍵字:

EDA FPGA QuartusⅡ 數字鐘

圖像傳感器,或稱感光元件,是一種將光學圖像轉換成電子信號的設備,它被廣泛地應用在數碼相機和其他電子光學設備中。早期的圖像傳感器采用模擬信號,如攝像管(video camera tube)。如今,圖像傳感器主要分為感光耦合元件(charge-coupled device, CCD)和互補式金屬氧化物半導體有源像素傳感器(CMOS Active pixel sensor)兩種。本文介紹基于CMOS或CCD兩種圖像傳感器的應用及技術文獻,供大家參考。

基于USB傳輸及CMOS圖像傳感器的指紋識別儀的實

關鍵字:

Verilog HDL QuartusⅡ VHDL

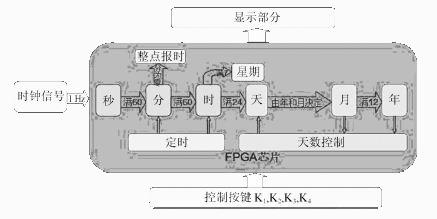

基于FPGA設計數字日歷可以實現以軟件方式設計硬件的目的,無需購買專用數字芯片,從而克服了傳統利用多片數字集成電路設計數字日歷存在焊接麻煩、調試繁瑣、成本較高等問題。而且,基于FPGA的數字日歷與傳統系統相比,在設計靈活、開發速度、降低成本、計時精度、功能實現上都得到大幅度提升,能夠更好地滿足人們日常生活的需要。

本文介紹如何利用VHDL硬件描述語言設計一個具有年、月、日、星期、時、分、秒計時顯示功能,時間調整功能和整點報時功能的數字日歷。在QuartusⅡ開發環境下,采用自頂向下的設計方法,建

關鍵字:

FPGA QuartusⅡ

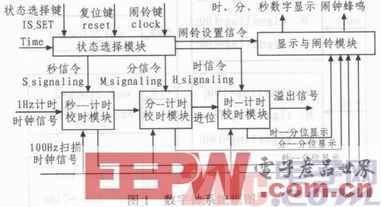

摘要:采用FPGA進行的數字電路設計具有更大的靈活性和通用性,已成為目前數字電路設計的主流方法之一。本文給出一種基于FPGA的數字鐘設計方案。該方案采用VHDL設計底層模塊,采用電路原理圖設計頂層系統。整個系統在QuartusⅡ開發平臺上完成設計、編譯和仿真,并在FPGA硬件實驗箱上進行測試。測試結果表明該設計方案切實可行。

EDA(Electronic Design Automation)又名電子設計自動化,其基本特征是:以超大規模可編程邏輯器件,如FPGA,為設計載體,以硬件描述語言,如VHDL,為

關鍵字:

FPGA QuartusⅡ

針對實現傳統模糊PID控制器時,需要建立比例、積分和微分三個模糊控制器,存在模糊規則較繁雜、運算量大、速度慢等問題,提出了以PD模糊控制器代替P1模糊控制器,采用兩個PD模糊控制器,并引入FPGA技術,實現模糊PID控制器。通過QuartusⅡ和Matlab聯合仿真,比較了基于FBC和SBC實現的模糊PID控制器的控制效果,驗證了設計方案的正確性和可行性。

關鍵字:

模糊PID 控制器 FPGA:QuartusⅡ Matlab

1 引言

隨著FPGA向低成本、低功耗、高性能方向發展,其I/O引腳大多采用微間距TOFP或BGA封裝工藝,因而使引出多種內部信號的I/O引腳以及FPGA的驗證工作變得非常困難,同時FPGA的驗證和調試耗時占總開發時間的50%以上。

在驗證和調試系統時,傳統上是把信號線引到I/O引腳,然后采用示波器、邏輯分析儀或總線分析儀進行測量和分析。由于這些設備相當昂貴,而且調試時又需要許多連線夾,因此一不小心就會燒壞器件或電路板。

伴隨著EDA 工具的快速發展,Altera公司在Quartus

關鍵字:

FPGA I/O EDA QuartusⅡ 存儲

電子產品世界,為電子工程師提供全面的電子產品信息和行業解決方案,是電子工程師的技術中心和交流中心,是電子產品的市場中心,EEPW 20年的品牌歷史,是電子工程師的網絡家園

關鍵字:

DSP FPGA FIR QuartusⅡ

quartusⅡ介紹

您好,目前還沒有人創建詞條quartusⅡ!

歡迎您創建該詞條,闡述對quartusⅡ的理解,并與今后在此搜索quartusⅡ的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473