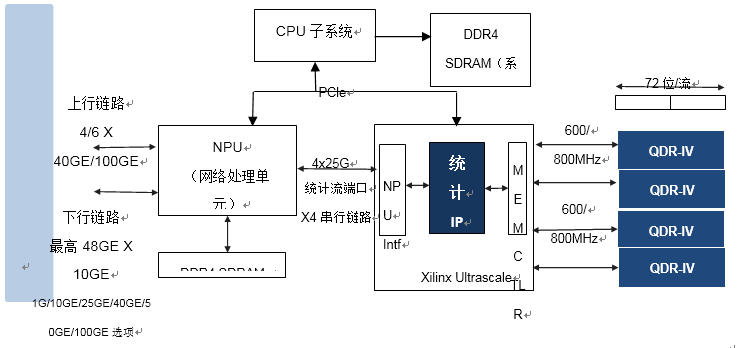

- 網絡路由器帶有用于性能監控、流量管理、網絡追蹤和網絡安全的統計計數器。計數器用來記錄數據包到達和離開的次數以及特定事件的次數,比如當網絡出現壞包時。數據包的到達會使多個不同的統計計數器發生更新;但一臺網絡設備中的統計計數器的數量及其更新速度常常受到存儲技術的限制。 管理統計計數器需要高性能的存儲器才能滿足多重的讀—修改—寫操作。本文將描述一種使用IP方法的獨特統計計數器,這種計數器的一端可以連接網絡處理器(NPU),另一端可以連接Xilinx公司的QDR-IV存儲控制器。QDR-IV統計計數器IP是

- 關鍵字:

QDR-IV IP

- 在本系列第二部分,我們探討了總線轉換、總線翻轉、地址奇偶校驗等重要的總線問題。在第三也是最后一部分,我們將探討校正問題,其中包括矯正訓練、控制/地址信號校正和讀寫校正,以及糾錯碼(ECC)和QDR-IV存儲器控制器的設計建議。 校正訓練序列 存儲器控制器和QDR IV較高的工作頻率意味著數據有效窗口很窄。QDR-IV器件支持“校正訓練序列”,它可通過減少字節通道之間的偏差擴大這個窗口,從而在控制器讀取存儲器的數據時,增加時序余量。校正訓練序列是賽普拉斯的QDR-IV SRAM的

- 關鍵字:

QDR-IV SRAM

- 總線轉換的注意事項 總線轉換時間非常重要,其決定了讀和寫指令間是否需要額外的間隔來避免在同一個I/O 端口上發生總線沖突。 想象下QDR-IV HP SRAM 中端口A 先后收到寫指令和讀指令。從CK 信號的上升沿(與初始化寫指令周期相對應)算起,在整整三個時鐘周期后向DQA 引腳提供寫數據。讀數據則將在下一個周期發送,因為 DQ從CK 信號的上升沿(與初始化讀指令的周期相應)算起五個時鐘周期后才能獲得數據。

- 關鍵字:

QDR-IV SRAM

- 流媒體視頻、云服務和移動數據推動了全球網絡流量的持續增長。為了支持這種增長,網絡系統必須提供更快的線路速率和每秒處理數百萬個數據包的性能。在網絡系統中,數據包的到達順序是隨機的,且每個數據包的處理需要好幾個存儲動作。數據包流量需要每秒鐘訪問數億萬次存儲器,才能在轉發表中找到路徑或完成數據統計。 數據包速率與隨機存儲器訪問速率成正比。如今的網絡設備需要具有很高的隨機訪問速率(RTR)性能和高帶寬才能跟上如今高速增長的網絡流量。其中,RTR是衡量存儲器可以執行的完全隨機存儲(讀或寫)的次數,即隨機存儲速

- 關鍵字:

QDR-IV SRAM

- 靜態隨機存取存儲器市場領導者賽普拉斯半導體公司日前宣布,量產業界首款四倍速(QDR?-IV?)SRAM。賽普拉斯的QDR-IV?SRAM有144和72-Megabit?(Mbit)兩種容量,可滿足下一代交換機和路由器的100-400?Gigabit線卡對隨機傳輸速率的要求。賽普拉斯的QDR-IV?SRAM是市場上性能最高的標準網絡存儲器解決方案。 對于不斷提升的線卡和交換速率來說,RTR(每秒完整隨機存取次數)是存儲器性能的重要指標。提升線卡速率的瓶

- 關鍵字:

賽普拉斯 SRAM QDR-IV

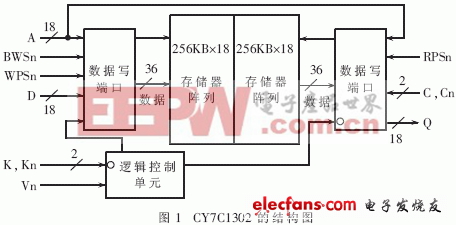

- QDR SRAM與Spartan3 FPGA的接口設計,為了滿足當前系統和處理器的生產量需求,更新的靜態存儲器應運而生。QDR SRAM就是由Cypress、Renesas、IDT、NEC和Samsung為高性能的網絡系統應用而共同開發的一種具有創新體系結構的同步靜態存儲器。 1 QDR SRAM的

- 關鍵字:

接口 設計 FPGA Spartan3 SRAM QDR

- 北京訊,包括賽普拉斯半導體公司(NASDAQ:CY)和瑞薩電子公司(TSE: 6723)在內的QDR聯盟日前宣布推出業界最快的四倍數據率(QDR) SRAM(靜態隨機存取存儲器)。這些新型存儲器將被命名為QDRII+ Xtreme并將以高達633兆赫茲(MHz)的時鐘頻率允許。這些器件將與現有的QDR II+器件在管腳、尺寸和功能方面兼容,從而使網絡交換機、路由器及聚合平臺制造商不必修改電路板設計,只需提高系統內時鐘速度即可大幅改善產品性能。

- 關鍵字:

QDR SRAM

qdr介紹

您好,目前還沒有人創建詞條qdr!

歡迎您創建該詞條,闡述對qdr的理解,并與今后在此搜索qdr的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473