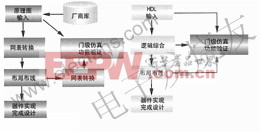

- FPGA/EPLD的自上而下設(shè)計方法,FPGA/EPLD的自上而下(Top-Down)設(shè)計方法: 傳統(tǒng)的設(shè)計手段是采用原理圖輸入的方式進(jìn)行的,如圖1所示。通過調(diào)用FPGA/EPLD廠商所提供的相應(yīng)物理元件庫,在電路原理圖中繪制所設(shè)計的系統(tǒng),然后通過網(wǎng)表轉(zhuǎn)換產(chǎn)生某一特

- 關(guān)鍵字:

FPGA EPLD 自上而下 設(shè)計方法

- FPGA/EPLD的自上而下(Top-Down)設(shè)計方法:傳統(tǒng)的設(shè)計手段是采用原理圖輸入的方式進(jìn)行的,通過調(diào)用FPGA/EPLD廠商所提供的相應(yīng)物理元件庫,在電路原理圖

- 關(guān)鍵字:

FPGA EPLD 自上而下

- FPGA/EPLD的自上而下設(shè)計方法及其優(yōu)缺點介紹,FPGA/EPLD的自上而下(Top-Down)設(shè)計方法: 傳統(tǒng)的設(shè)計手段是采用原理圖輸入的方式進(jìn)行的,如圖1所示。通過調(diào)用FPGA/EPLD廠商所提供的相應(yīng)物理元件庫,在電路原理圖中繪制所設(shè)計的系統(tǒng),然后通過網(wǎng)表轉(zhuǎn)換產(chǎn)生某一特

- 關(guān)鍵字:

缺點 介紹 及其 方法 自上而下 設(shè)計 FPGA/EPLD

- 在同步串行數(shù)據(jù)傳輸過程中,時鐘線上只要有一點小毛刺就會導(dǎo)致數(shù)據(jù)傳輸失誤,從而影響系統(tǒng)的正常工作。傳統(tǒng)...

- 關(guān)鍵字:

濾波器 EPLD 干擾信號

- FPGA/EPLD的自上而下設(shè)計方法,FPGA/EPLD的自上而下(Top-Down)設(shè)計方法: 傳統(tǒng)的設(shè)計手段是采用原理圖輸入的方式進(jìn)行的,如圖1所示。通過調(diào)用FPGA/EPLD廠商所提供的相應(yīng)物理元件庫,在電路原理圖中繪制所設(shè)計的系統(tǒng),然后通過網(wǎng)表轉(zhuǎn)換產(chǎn)生某一特

- 關(guān)鍵字:

方法 設(shè)計 自上而下 FPGA/EPLD

- 1問題的提出

在同步串行數(shù)據(jù)傳輸過程中,時鐘線上只要有一點小毛刺就會導(dǎo)致數(shù)據(jù)傳輸失誤,從而影響系統(tǒng)的正常工作。傳統(tǒng)的處理方法是在接收端并入一小電容來濾除毛刺,這種方法只能去除某一固定頻率下的干擾,

- 關(guān)鍵字:

EPLD 抗干擾濾波器

- 隨著VLSI/ULSI技術(shù)的發(fā)展,可編程邏輯器件EPLD/FPGA越來越受到人們的青睞,由于它具有集成度高、速度快、開發(fā)周期短、費用低、用戶可定義功能及可重復(fù)編程和擦寫等許多優(yōu)點,其應(yīng)用領(lǐng)域不斷擴大。這些器件的靈活性和

- 關(guān)鍵字:

EPLD PCI 總線 仲裁器

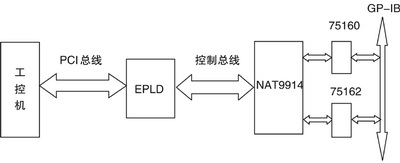

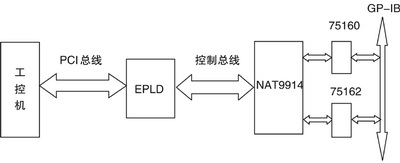

- PCI總線自其問世以來,以其諸多優(yōu)點,在當(dāng)今的計算機系統(tǒng)中得到了廣泛應(yīng)用,已經(jīng)成為計算機設(shè)備的標(biāo)準(zhǔn)接口。本文在認(rèn)真分析PCI總線的接口信號和接口時序的基礎(chǔ)上,利用EPLD器件設(shè)計實現(xiàn)了PCI總線接口。由于EPLD器件支

- 關(guān)鍵字:

EPLD PCI 總線 接口設(shè)計

- 主要介紹作為從設(shè)備如何根據(jù)PCI總線協(xié)議設(shè)計PCI總線接口電路,從而實現(xiàn)基于PCI總線的GP-IB接口電路設(shè)計,重點闡述PCI總線接口狀態(tài)機的設(shè)計。

- 關(guān)鍵字:

PCI 狀態(tài)機 GP-IB EPLD 200806

- 摘 要:用EPLD實現(xiàn)的單脈沖二次雷達(dá)應(yīng)答處理器。其主要功能包括:應(yīng)答框架脈沖檢測,應(yīng)答信息解碼,將應(yīng)答信息裝配成飛機的同步應(yīng)答組形成目標(biāo)報告,丟棄非同步虛假應(yīng)答。

關(guān)鍵詞:單脈沖二次雷達(dá)? 應(yīng)答模式? EPLD

1 一次雷達(dá)與二次雷達(dá)

二次雷達(dá)與一次雷達(dá)基本上是并行發(fā)展的。與一次雷達(dá)相比,二次雷達(dá)有回波強、無目標(biāo)閃爍效應(yīng)、詢問波長與應(yīng)答波長不等的特點,從而消除了地物雜波和氣象雜波的干擾。單脈沖技術(shù)應(yīng)用于二次雷達(dá),可以方便地基于多個波束對目標(biāo)測量,進(jìn)而有效地增加數(shù)

- 關(guān)鍵字:

EPLD 單脈沖二次雷達(dá) 應(yīng)答模式

epld介紹

EPLD EPLD: Erasable Programmable Logic Device(可擦除可編輯邏輯器件)可擦除可編程邏輯器件(EPLD)是一種集成電路,包括一系列的編程邏輯器件,其無需進(jìn)行再次連接。

1、PLD器件的設(shè)計步驟

1.電路邏輯功能描述

PLD器件的邏輯功能描述一般分為原理圖描述和硬件描述語言描述,原理圖描述是一種直觀簡便的方法,它可以將現(xiàn)有的小規(guī)模集成 [

查看詳細(xì) ]

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473