- 秘訣在我們的實現中,PC不會向FPGA發送任何位置或速度信息。 相反,它會發送加速度和時間信息。 FPGA 使用積分器將它們轉換為速度和位置(并相應地驅動階躍/二極管信號)。因此,我們的運動控制器充當加速度積分器。 這很容易實現,因為在FPGA中,積分器只是一個累加器。 以下“C”代碼說明了FPGA在每個時鐘周期的性能:??//?Acceleration?is?known?(provided?by?the?PC)

- 關鍵字:

FPGA CNC 步進電機 積分器

- 主要特性:· 羅氏線圈配套積分器· 對羅氏線圈二次側輸出信號進行積分處理· 線性誤差低于0.1%· 與LEM的ART和ARU系列羅氏線圈產品配套,為用戶提供計量和監測解決方案· DIN導軌安裝參數:· 從100A到5000A有12種原邊電流量程可選· 可配套從22.5mV/KA到120mV/KA 6種輸出的羅氏線圈?· 6種輸出類型可選: 4種真有效值輸出0-20mA, 4-20mA, 0-5V & 0-10V和2種瞬時電壓輸出0-225mV and 0-333mV· 可以通過2個按鈕進

- 關鍵字:

積分器

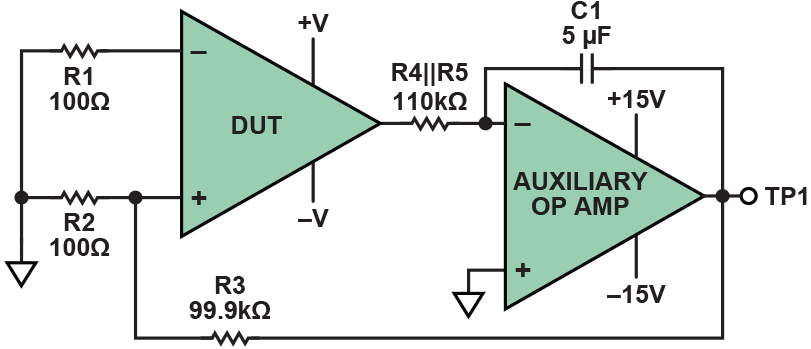

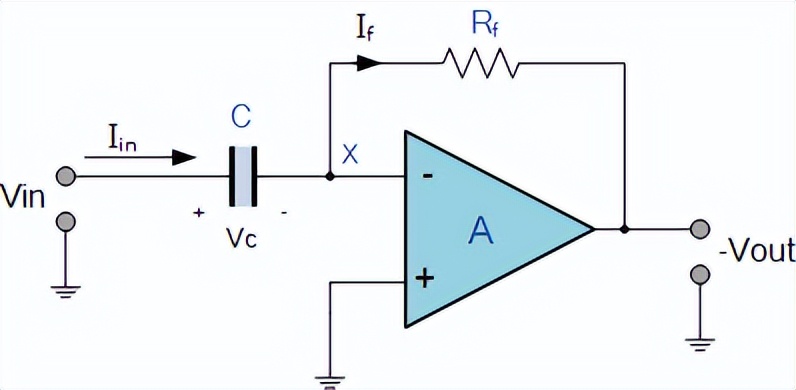

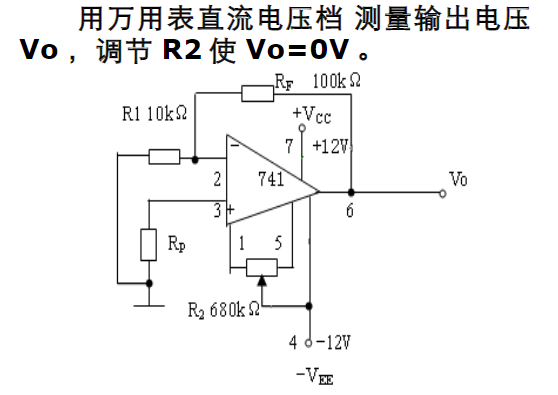

- 通過將電阻器用作增益調整設置元件,建立起了在 DC 情況下運算放大器 (op amp) 的傳輸函數。在一般情況下,這些元件均為阻抗,而阻抗中可能會包含一些電抗元件。下面來看一下圖 1 所示的這種一般情況。圖 1 運算放大

- 關鍵字:

運算放大器 積分器 電路分析

- 1引言在諸多的電力電子電路裝置中,常常需要具有復位功能的積分器,而市面上所售芯片中卻往往沒有現成的...

- 關鍵字:

開關 積分器 復位

- 通過將電阻器用作增益調整設置元件,建立起了在 DC 情況下運算放大器 (op amp) 的傳輸函數。在一般情況下,這些元件均為阻抗,而阻抗中可能會包含一些電抗元件。下面來看一下圖 1 所示的這種一般情況。圖 1 運算

- 關鍵字:

運算放大器 積分器 電路分析

- 摘 要:介紹一種基于ADSP21060和Virtex II的星載圖像處理系統。分析了圖像處理系統的功能和任務,給出了處理系統的硬件結構、FPGA的功能模塊、DSP的軟件框架和模塊。通過地面原理樣機開發,驗證了系統設計的正確性和高效性。關鍵詞:ADSP21060 Virtex II 圖像處理系統 積分器 乒乓結構

圖像處理系統多采用DSP陣列、DSP加FPGA/CPLD或單由FPGA/CPLD器件等方式構成。采用DSP陣列構成的圖像處理系統,其優點是處理功能可以通過軟件靈活修改,其缺點主要有功耗大、體積

- 關鍵字:

ADSP21060 II Virtex 單片機 積分器 乒乓結構 嵌入式系統 圖像處理系統

積分器介紹

????? 積分器就是能將輸入信號進行積分運算的元件。把集成運算放大器接成能實現輸出電壓與輸入電壓對時間的積分成正比的放大電路。它廣泛用于波形變換、延時等環節中,是信號處理系統中的重要單元電路。在數學上積分是求取某一曲線下面積的過程。如矩形法:就是把曲邊梯形分成若干個窄曲邊梯形,然后用窄矩形來近似代替窄曲邊梯形,從而求得定積分的近似值。 在物理上的積分是一種能夠執行積分運算的電路,其輸出信號為輸 [

查看詳細 ]

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473