- 西門子數字化工業軟件近日推出 Tessent? RTL Pro 創新軟件解決方案,旨在幫助集成電路 (IC) 設計團隊簡化和加速下一代設計的關鍵可測試性設計 (DFT) 任務。隨著 IC 設計規模不斷增大、復雜性持續增長,工程師需要在設計早期階段發現并解決可測試性問題,西門子的 Tessent 軟件可以在設計流程早期階段分析和插入大多數 DFT 邏輯,執行快速綜合,運行 ATPG(自動測試向量生成),以發現和解決異常模塊并采取適當的措施,滿足客戶不斷增長的需求。Tessent RTL Pro 進一步擴展了

- 關鍵字:

西門子 Tessent RTL Pro 可測試性設計

- 西門子數字化工業軟件近日推出Tessent Multi-die軟件解決方案,旨在幫助客戶加快和簡化基于2.5D和3D架構的新一代集成電路(IC)關鍵可測試性設計(DFT)。隨著市場對于更小巧、更節能和更高效能的IC需求日益提升,IC設計界也面臨著嚴苛挑戰。下一代組件正傾向于采用復雜的2.5D和3D架構,以垂直(3D IC)或并排(2.5D)方式連接多個晶粒,使其能夠作為單一組件運作。但是,這種做法為芯片測試帶來巨大的挑戰,因為大部分傳統的測試方法都是基于常規的2D流程。為了解決這些挑戰,西門子推出Tess

- 關鍵字:

西門子 2.5D 3D 可測試性設計

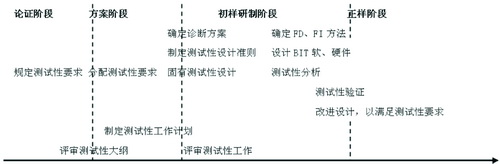

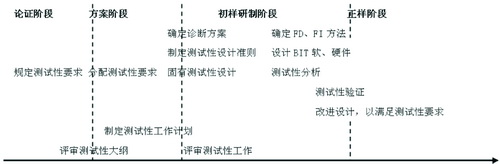

- 從系統測試性設計的角度,分析了國內外測試性設計技術的發展狀況、存在的問題;討論了開展系統測試性設計并制定測試性工作規范在飛行器設計中的必要性;總結了系統測試性設計的一般工作流程;并根據航天產品特點,對測試性設計方法進行探索研究。

- 關鍵字:

系統測試 系統級 可測試性設計 飛行器 200806

- 摘 要: 本文論述了邊界掃描技術的基本原理和邊界掃描在電路板測試及在FPGA、DSP器件中的應用。介紹了為提高電路板的可測試性而采用邊界掃描技術進行設計時應注意的一些基本要點。關鍵詞: 邊界掃描測試;JTAG;電路板測試;可測試性設計引言電子器件的生產商和電子產品的制造商都在傾向于采用最新的器件技術,如BGA、CSP(芯片規模封裝)、TCP(倒裝芯片封裝)和其它更小的封裝,以提供更強的功能、更小的體積,并節省成本。電路板越來越密、器件越來越復雜、電路性能要求越來越苛刻,越來越難的接入問題導致了工業標準

- 關鍵字:

JTAG 邊界掃描測試 電路板測試 可測試性設計 PCB 電路板

可測試性設計介紹

您好,目前還沒有人創建詞條可測試性設計!

歡迎您創建該詞條,闡述對可測試性設計的理解,并與今后在此搜索可測試性設計的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473