基于Actel FPGA的PWM IP的應用

(2) PWM的優點

本文引用地址:http://www.j9360.com/article/97920.htmPWM的優點是從處理器到被控系統信號都是數字形式的,無需進行數模轉換。讓信號保持為數字形式可將噪聲影響降到最小,噪聲只有在強到足以將邏輯1改變為邏輯0或將邏輯0改變為邏輯1時,才能對數字信號產生影響。這也是在某些時候將PWM用于通信的主要原因,從模擬信號轉向PWM可以極大地延長通信距離。在接收端,通過適當的RC或LC網絡可以濾除調制高頻方波并將信號還原為模擬形式。

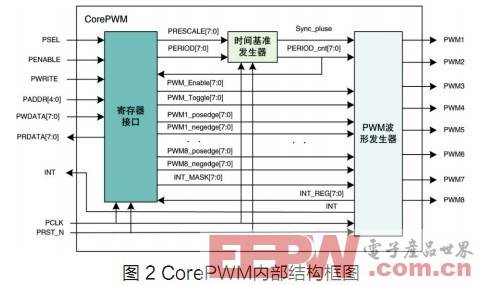

(3) CorePWM的結構框圖

CorePWM的內部結構框圖如圖 2所示。它主要由時間基準發生器、PWM波形發生器和寄存器接口等模塊組成。

● 時間基準發生器:接收PRESCALE和PERIOD寄存器的值,并產生一個0~255的周期計數。

● PWM波形發生器:用輸入周期計數器和上升、下降沿寄存器的值進行比較,當計數值等于任何一個邊沿寄存器的值的時候,就會產生一個相應的PWM波形輸出,并且中斷寄存器將會被更新。

● 寄存器接口:主要是提供PWM內核的APB總線協議的接口。

pwm相關文章:pwm原理

評論