FPGA在彈上信息處理機中的應用

(6)發送

本文引用地址:http://www.j9360.com/article/93424.htm數據融合表的發送則由“發送狀態機(SendSTM) IP”完成。它以數據融合表FIFO、2.56M發送時鐘為輸入,一旦啟動就不再停止。發送狀態機首先查詢數據融合表FIFO, 若FIFO為空,則等待;若FIFO不空,則以2.56M/8的固定時鐘頻率持續讀取數據融合表FIFO的數據,再送入“15段加擾器”進行加擾,加擾后的數據和時鐘經RS-422驅動電路轉化為RS-422差分形式發送給加密器,即2.56M輸出。

(7)1.28M同步輸入串口故障檢測

FPGA中的故障檢測單元(FDU)負責檢測1.28M同步輸入串口的輸入信號是否正常。當故障檢測單元FDU發現1.28M同步輸入串口產生的SwitchBuf信號的周期和晶振產生的20ms時鐘周期誤差超過△T(如±2ms),則認為1.28M同步輸入串口故障,立即將SwitchBuf信號切換到由晶振分頻產生的20ms時鐘上。

系統仿真

以下為相關軟件對系統主要功能進行的仿真:

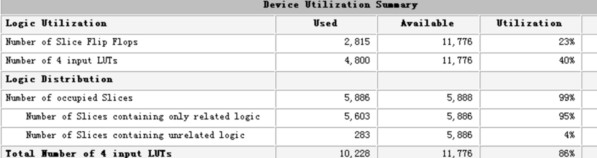

圖4 ISE編譯后得出的FPGA資源利用情況

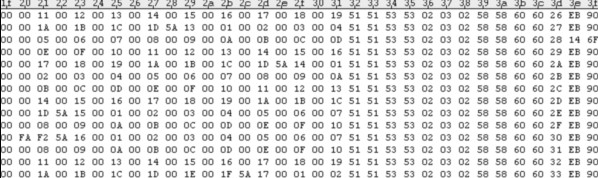

圖5 數據融合表的仿真結果

評論