IGLOO─業界極低功耗的FPGA

隨著半導體工藝的飛速發展和芯片工作頻率的提高,芯片的功耗迅速增加,而功耗增加又將導致芯片發熱量的增大和可靠性的下降。因此,功耗已經成為深亞微米集成電路設計中需要考慮的一個重要因素。為了使產品更具競爭力,工業界對芯片設計的要求已從單純追求高性能、小面積轉為對性能、面積、功耗的綜合要求。

本文引用地址:http://www.j9360.com/article/92555.htm芯片對功耗的苛刻要求源于產品對功耗的要求,由于集成電路的迅速發展和對消費類電子產品,特別是便攜式(移動)電子產品的需求日新月異,使得設計者對電池供電的系統已不能只考慮它優化的兩個方面——速度和面積,而必須要注意它已經表現出來的且變得越來越重要的第三個方面─功耗,這樣才能延長電池的壽命和電子產品的運行時間。

本文主要介紹基于FPGA功耗的相關知識,例如功耗的分類、功耗的組成、如何降低功耗以及選擇一個合適的低功耗器件等,讓讀者對FPGA的功耗具有感性的認識。

1.FPGA功耗的基本概念

(1) 功耗的組成

無論是FPGA還是MCU,功耗的一般都是由兩部分組成:靜態功耗和動態功耗,靜態功耗主要是由晶體管的漏電流引起,由源極到漏極的漏電流以及柵極到襯底的漏電流組成;動態功耗主要由電容充放電引起,其主要的影響參數是電壓、節點電容和工作頻率,可以用公式(1)表示。

P=α×CL×V2dd×f (1)

(2) 靜態功耗

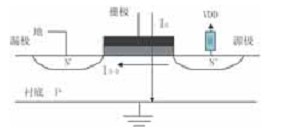

靜態功耗主要是由漏電流引起,漏電流是在芯片上電的時候,無論是處于工作還是處于靜止狀態,都一直會存在的一個電流,來源于晶體管的三個極,如圖1所示,它分為兩部分,一部分是來自源極到漏極的泄漏電流IS-D,另一部分是來自柵極到襯底的泄漏電流IG,漏電流與晶體管的溝道長度和柵氧化物的厚度成反比。

源極到漏極的泄漏電流IS-D:也稱為亞閥值電流,是泄漏的主要原因,我們都知道MOS管在關斷的時候,溝道阻抗非常大,但是再大都會有一個值,所以只要芯片供電必然會存在一個從源極到漏極的泄漏電流,隨著半導體工藝不斷先進,晶體管尺寸不斷減小,溝道長度也逐漸減小,使得溝道阻抗變小,從而IS-D變得越來越大,而且源極到漏極的漏電流隨溫度增加呈指數增長,例如:結溫從25℃上升到85℃時源極到漏極的泄漏電流會增加5倍之多。

柵極到襯底的泄漏電流IG:雖然沒有亞閥電流那么關鍵,但是也非常重要,柵極的漏電流隨著柵氧化物的厚度減小而增大,特別在65nm、45nm的技術中顯得尤為突出。

圖1 漏電流示意圖

評論