軟件無線電的功率:一種針對功率設計SDR的整體方法(07-100)

由于像美國聯合戰術無線電系統(JTRS)這樣的計劃,軟件定義的無線電(SDR)早已被證實。然而,有許多問題嚴重地制約著SDR的廣泛部署,其中相當重要的問題就是功率。

本文引用地址:http://www.j9360.com/article/91920.htm功率是在設計每一個SDR子系統時的主要考慮因素,特別是因為它們要消耗比硬件無線電更多的功率。例如,為了獲得預期的無線電通信距離(依賴于鏈路的狀況,典型值為5-10千米數量級),射頻(RF)前端必須具備足夠的發射功率。同樣,對于靠電池工作的無線電設備,RF前端、調制解調器和加密處理子系統的功耗都直接影響無線電設備的壽命。此外,對由調制解調器產生的熱量進行散熱的能力直接影響到無線電設備的壽命,并且甚至可能影響到能在機箱中同時處理的通道數,且有更多的影響。

因此,降低一個SDR的功率有許多好處,這些好處可能甚至包括通過購買更少的備用電池而降低運營費用。在此,為了獲得其中的一些好處,我們談論的重點將放在降低SDR調制解調器功耗的整體方法上。

降低功耗的硬件方法

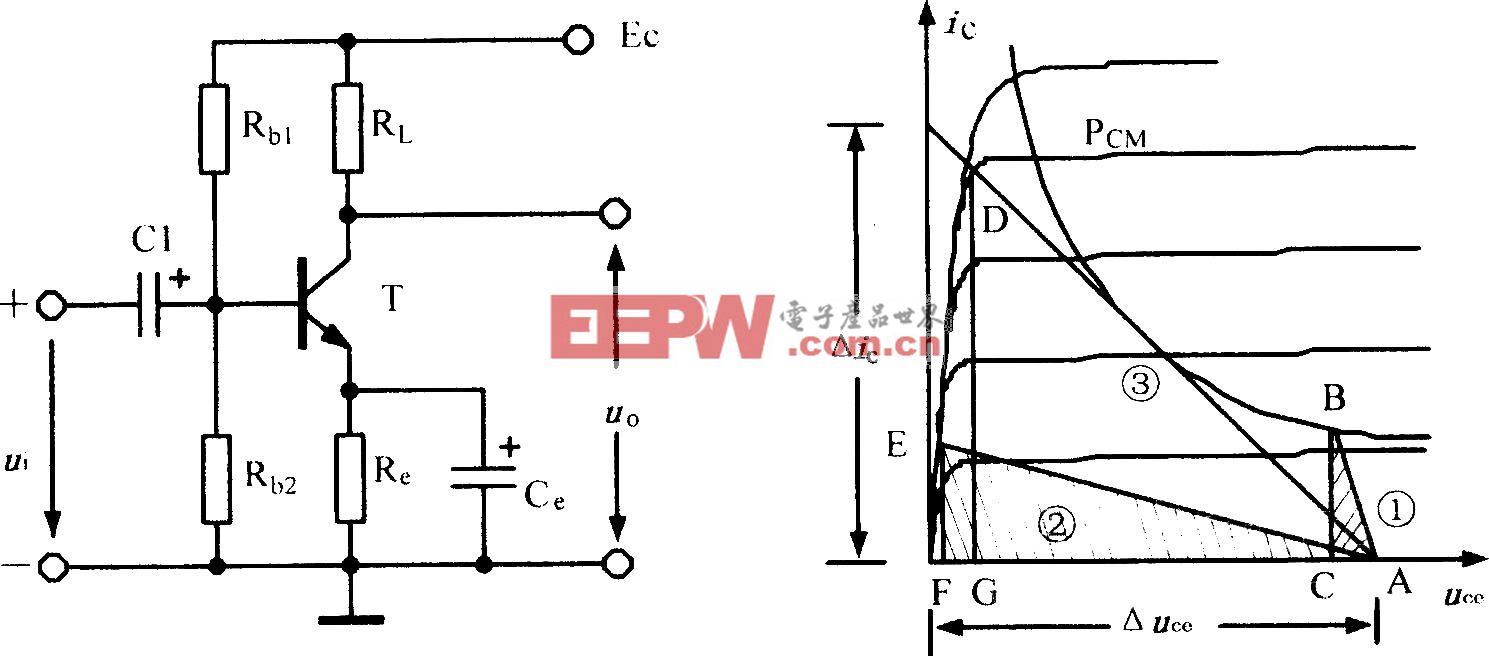

為了降低調制解調器中的功耗,大多數人首先注意的就是在處理過程中的硬件,其中,通常包含現場可編程門陣列(FPGA)、數字信號處理器(DSP)和通用目的處理器(GPP)。區分任何硬件器件的兩個功耗源—靜態功耗和動態功耗—是至關重要的。靜態功耗是一個已加電但不活躍的器件所消耗的固有功率,由晶體管的電流泄漏所控制。另一方面,動態功耗是由活躍使用的器件所消耗的功率,該功率受到若干變量的影響,包括電源電壓、對外部存儲器的訪問次數、數據帶寬等等。檢測兩種類型的功耗是至關重要的,特別是在無線電設備具有一個通常接收比發射更長的占空周期的情形下。在GPP和甚至DSP的情形下,像頻率調節、電壓調節和電源關閉模式這樣的電源管理功能已經變得日益普遍。然而,關于FPGA又是什么情況呢?

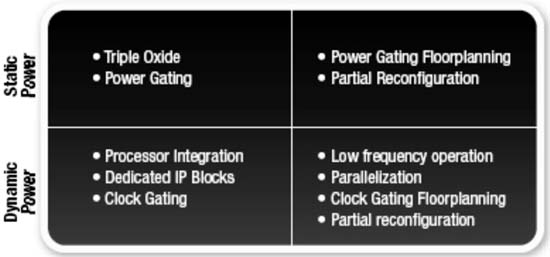

圖1 用于降低SDR功耗的一種真正的整體方法要采用來自每一個象限的多種技術。

有許多方法可以用來降低FPGA中的靜態或動態功耗,其中許多方法不是可以同時應用的。一些降低靜態功耗的方法包括三極柵氧化層電源門控。

評論