基于ADSP-TS201S的圖像采集處理系統(05-100)

引言

本文引用地址:http://www.j9360.com/article/91486.htm隨著人們對實時信號處理要求的不斷提高和大規模集成電路的迅速發展,作為數字信號處理核心和標志的數字信號處理器DSP芯片得到了快速的發展和應用。它不但可以廣泛應用于通信系統、圖形/圖像處理、雷達聲納、醫學信號處理等實時信號處理領域。就ADI公司而言,繼16-bit定點ADSP21xx和32-bit浮點ADSP21xxx系列之后,日前又推出了TigerSHARC系列的新型器件。本文介紹使用該系列中的ADSP-TS201S芯片實現一個圖像采集處理系統的設計方案。

系統總體方案

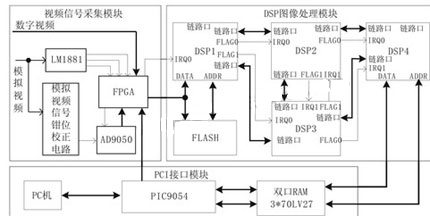

該系統可以完成圖像的采集、處理和顯示,從而實現目標識別與跟蹤的智能信號處理。該系統是對攝像機數字,模擬兩路視頻數據進行采集,處理后通過PCI總線在PC機上顯示出來。整個系統主要由視頻信號采集模塊、DSP圖像處理模塊、PCI接口模塊三個部分組成(圖1)。

圖1 圖像采集處理系統框圖

系統的各個功能模塊電路設計

·視頻信號采集模塊

攝像機提供兩路視頻信號:一路模擬視頻,一路數字視頻。

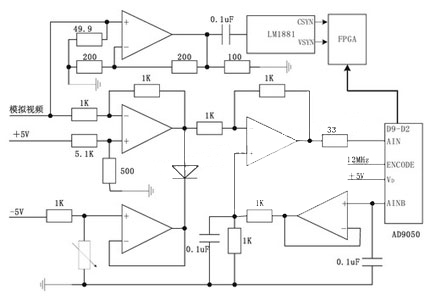

模擬視頻信號經過鉗位校正、放大后,將信號送入到A/D轉換器,再經FPGA鎖存后將視頻信號發送給DSP1;經視頻同步分離電路,由LM1881分離出模擬視頻的行、場同步信號,用于控制視頻數據采集到DSP1,以便進行圖像處理。鉗位校正、視頻同步電路如圖2所示。模擬視頻經運放輸入,將中心電平調到3.3V,加到A/D輸入端。A/D轉換后的數據進入FPGA鎖存。運放均采用ADI公司的AD8047AR,A/D轉換器采用ADI公司的AD9050。AD9050為10位A/D轉換器,取其高8位進入FPGA。采樣時鐘12MHz,與數字視頻信號相同。由FPGA對48MHz時鐘四分頻產生。

圖2 模擬視頻輸入轉換電路

評論