Ge組分對SiGe HBT主要電學特性的影響

0 引言

本文引用地址:http://www.j9360.com/article/89319.htmSiGe基區異質結雙極型晶體管(SiGe HBT)是利用SiGe合金特性制成的器件。自1987年采用MBE技術首次制作出SiGe基區HBT以來,SiGe集成電路的規模和電路的速度不斷發展,電流增益和頻率響應等性能已經接近或達到了化合物異質結器件的水平。而SiGe異質結技術和傳統的Si集成電路相比,在工藝上并未增加大的復雜性,且成本低于化合物半導體器件。最新的SiGe HBT的研究表明已研制出超過200 GHz電流增益峰值達到400的晶體管,并且低溫下fT達到200 GHz的SiGeHBT也已制成。

Ge的電子遷移率是Si的2.6倍,空穴遷移率達到Si的3.5倍。而器件的速度最終取決于在一定的電壓下載流子被"推動"而通過器件的速度。通過對SiGe HBT的結構和工藝參數的設計,可以定向地對SiGe HBT的能帶結構進行剪裁,在器件結構設計中使用Si1-xGex薄膜作基區,發射結的帶隙寬度變化使電子注入基區的勢壘降低,使發射效率提高,電流增益增大。通過對基區Ge分布的設計使得基區產生一個內建電場,減小載流子的基區渡越時間從而使fT得到提高,制成超高頻晶體管。因此如何通過設計器件結構和控制Ge的組分,包括對Si1-xGex合金的x值的選擇和對Ge分布形狀的設計,使器件獲得更好的電學特性,充分發揮異質結半導體器件的特性成為這一領域研究的重點之一。

綜上所述,SiGe HBT的電學特性參數fT和β與Ge的含量和分布關系密切,本文通過計算分析,得到SiGe HBT中Ge的組分和含量對其主要電學特性的影響。

1 Si/Si1-xGex異質結與SiGe HBT

1.1 Si1-xGex異質結

在異質結晶體管中基區采用帶隙寬度較小的半導體材料,而發射區采用帶隙寬度較大的半導體材料,可以使器件獲得高的發射效率。通過改變異質結中兩種材料的組分,改變材料的結構和帶隙寬度,使結的過渡漸變,引起導帶和價帶產生能量梯度,則帶隙寬度的漸變產生的等效內建電場使載流子的渡越時間減小。對于SiGe HBT,通過對基區Ge組分的設計在基區形成內建場,減小載流子基區渡越時間,進一步提高器件的速度。

Si的帶隙寬度為1.11 ev,Ge的帶隙寬度為0.67eV,用化學氣相沉積(CVD)的方法通過控制氣體比例可以獲得Si1-xGex合金,合金的帶隙寬度在0.67~1.11 eV。很多晶體管參數都與能帶結構有著直接的關系,而Si1-xGex合金綜合了Si和Ge各自能帶的特點,故會對其特性有較大的改善,而且由于Si1-xGex的帶隙寬度較小,適合于作HBT的基區以提高發射效率。

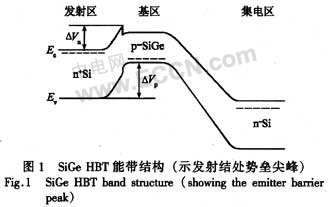

在兩種半導體的界面上,由于存在著帶隙的差異,如圖1所示,其能帶會在導帶底或價帶頂出現不連續的情況,導帶底出現的勢壘尖峰會阻止非平衡少數載流子(電子)由發射極的注入,從而會降低發射效率γ。但越過勢壘尖峰的電子會獲得更高的能量,在基區有更高的速度,可以改善器件的頻率特性。

對于晶體管的設計,需要在相互關聯的性能因素中進行折中考慮,為了縮短基區渡越時間提高晶體管的截止頻率,需盡量減小基區寬度。而當基區寬度減小時,器件會受到基區穿通效應的限制,在集電結耗盡層隨反偏電壓的增高和發射結耗盡層相連時(基區寬度變為零),發生基區穿通。而耗盡層寬度受摻雜濃度影響,增加基區摻雜濃度可以減小耗盡層的厚度,防止基區穿通的發生,但是隨著摻雜濃度的提高,發射效率會降低,提高了基區的摻雜濃度,發射區的摻雜濃度也需相應地提高,否則會造成電流增益的下降。而SiGe HBT的基區材料帶隙較窄,發射區材料帶隙較寬,在進一步提高基區的摻雜濃度時不會對電流增益產生大的影響。

1.2 Si1-xGex薄膜

為了保證器件載流子的遷移率,需要小心地外延Si1-xGex薄膜,Si和Ge的晶格常數相差約為4%。對于Si1-xGex合金,當其薄膜厚度較小,Ge含量較低時,Si1-xGex薄膜中價鍵處于一種畸變的狀態,晶格發生彈性應變,以贗晶形式生長,晶格失配較小,不會產生位錯失配,彈性應力將保持薄膜的穩定。而當薄膜厚度到達一定程度之后,贗晶體體內積累的應力增大到一定程度時,就會因晶面滑移而形成位錯失配,所以要保證薄膜的厚度在不產生位錯的范圍內。圖2為SiGe薄膜臨界有效厚度曲線圖。在制造工藝中,熱氧化工藝、熱擴散摻雜等工藝技術需要的溫度較高,離子注入摻雜后需要進行退火處理,這對Si1-xGex合金的熱穩定性也有一定要求。

超高真空化學氣相沉積(UHV/CVD)是在低壓化學氣相沉積(LPCVD)的基礎上,把超高真空技術與化學氣相沉積技術相結合,進一步發展出的一種新型異質結生長技術。UHV/CVD外延過程本質上屬于反應速率控制生長速率,可以實現均勻性、重復性、可控性良好的多片生長。采用UHV/CVD技術沉積的Si1-xGex薄膜,其中Ge的含量同氣源中的Ge含量可以成線性關系,可以由0%~100%任意變化,而HBT復雜的Ge組分分布需通過計算機控制GeH4流量來實現,以獲得厚度較均勻的薄膜,另外UHV/CVD加工溫度約550℃,不會造成更多的晶格缺陷,保證了載流子的遷移率。

在晶體管設計中,為了減少載流子的基區體復合,增加電子(非平衡少數載流子)擴散通過基區的比例,基區的有效寬度需要遠小于電子在基區中的擴散長度(Wb≤Lnb)。在SiGe HBT的設計中為了獲得更優良的器件性能需要增加Ge的含量,同時還要保證薄膜的穩定性,以免在工藝過程中受晶格失配的影響。這就要求在不會發生基區穿通的前提下進一步地降低Si1-xGex的薄膜厚度,這也符合晶體管設計對基區寬度小于電子在基區擴散長度的要求。

2 Si1-xGex合金中的Ge組分(x)設計

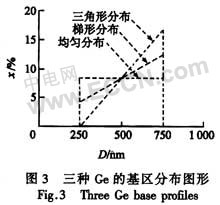

以往的研究指出了三種典型的Ge在基區的分布,分別是三角形分布、均勻分布和梯形分布,如圖3所示,而使用何種Ge分布圖形受器件的具體應用影響。圖3中D為由表面到器件體內的深度。可以看到,對于受到基區渡越時間限制的器件,可以使用緩變基區Ge分布獲得一個內建場。

在現代的雙極晶體管技術中,一般采用多晶硅發射極結構提高發射效率、電流增益和頻率響應。在SiGe HBT中使用多晶硅發射極可以減小發射區的渡越時間,而重摻雜的集電區則可以減小集電區的渡越時間,但是當基區寬度減小時,載流子在基區的渡越時間自然會減小,發射區的渡越時間變得更為重要,基區Ge均勻分布的器件速度更快。

為了獲得更好的器件性能,在Ge分布圖形設計時使用均勻與緩變相結合的方式,綜合二者的優點,可以使用梯形分布。對于不同的應用可以采用不同的分布來達到相應的要求,在要求精度較高的領域,如精確電流源,在數-模和模-數轉換器中,電流增益和Early電壓之積就較為重要;而在高頻應用中,如高頻放大器、振蕩器等,最高振蕩頻率就更為重要。

3 Ge的基區組分對器件特性的影響

不同結構參數、不同工藝的Si BJT有著不同的特性參數。SiGe HBT的基區是通過外延生長而成的,在實際應用當中器件是三維的,在電路中會有各種寄生參數,其理論計算會因維數增加變得復雜乃至難以進行。所以,在對器件特性參數進行理論推導時可以認為兩種器件的結構是相同的,以簡化計算,而且對一維本征器件進行理論推導建模會容易得到Ge的分布情況與器件特性之間的關系。

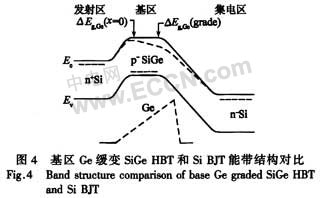

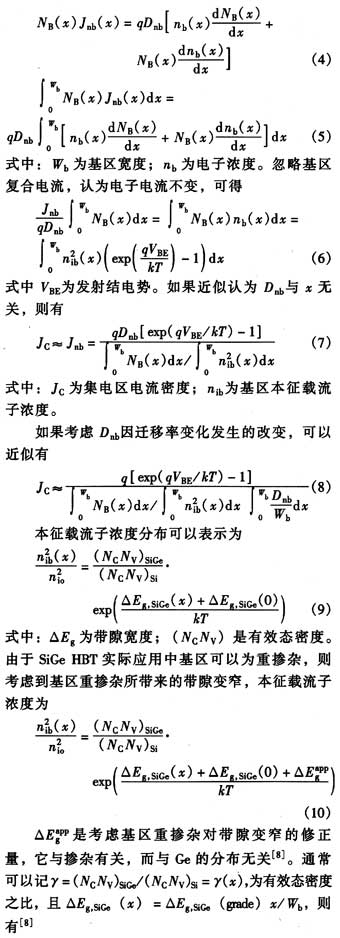

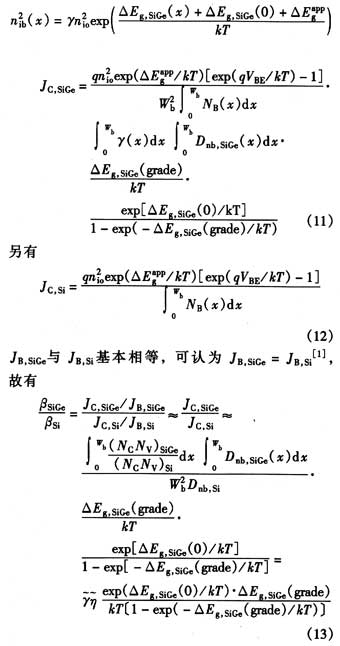

3.1 集電極電流和電流增益

在晶體管基區加入Ge對晶體管直流特性的影響主要是在集電極電流密度上。從物理上來看,電子在EB結處注入基區的勢壘,由于Ge的引入而降低,從而對于某一固定的EB偏置,發射區到集電區可以獲得更多的電荷輸運。圖4為基區Ge緩變SiGe HBT和Si BJT能帶結構的對比。

式(13)表明β與帶隙寬度變化的指數關系,引入Ge使得對于不同的應用可以更容易地獲得不同的β值,例如可以適當增大發射結處的Ge組分以增大上式中的分子而增大電流增益;適當減小集電結處的Ge組分以增大該處的帶隙寬度,從而使上式中的分母減小,而進一步提高電流增益,減小集電結處的Ge組分會減弱在基區形成的內建場,在速度要求不高而電流增益要求較大的應用場合可以采用這種方法。另外由式(13)可知Ge的組分對β的影響呈指數關系,Ge的組分變化可影響到β,而摻雜濃度的影響相對減小,在對β要求不高的應用中也可以提高基區的摻雜濃度來減小基區電阻而β不會有明顯的下降。

3.2頻率特性

SiGe HBT的特征頻率fT的表達式和Si-BJT是相同的,即為

可知,提高基區Ge的含量可以提高SiGe HBT的特征頻率,通過對Ge組分的設計可以在基區形成一個自建場,使載流子在基區加速,減小載流子基區渡越時間,提高頻率響應。

在SiGe HBT中,允許提高基區的摻雜濃度,則在保證基區不發生穿通的前提下,能夠盡量減小基區薄膜厚度(基區寬度),從而減小基區渡越時間提高頻率特性。另外利用一些工藝技術,如多晶硅發射區自對準技術可使基區串聯電阻(包含接觸電阻)降低,提高最高振蕩頻率。

4結論

本文對SiGe技術和Si/Si1-xGex異質結特性進行了分析,研究了對基區Ge組分進行優化設計的方向,對器件主要直流特性參數電流增益等進行了推算,獲知Ge的組分對β的影響呈指數關系。根據這一關系,在保證Si1-xGex薄膜穩定性的前提下,可以適當減小集電結處的Ge組分以增大該處的帶隙寬度,提高電流增益。而減小集電結處的Ge組分會減弱在基區形成的內建場,在速度要求不高情況下也可以用來提高電流增益。通過提高基區Ge的含量和對Ge組分的設計,提高載流子遷移率,在基區形成自建場,可以提高SiGe HBT的頻率特性。在SiGe HBT的設計時需綜合考慮薄膜穩定性,Ge組分對電流增益和頻率響應的影響,需要在薄膜穩定性與各種晶體管特性參數之間作折中考慮。

評論