基于C8051F的動平衡測試系統

0 引言

本文引用地址:http://www.j9360.com/article/87320.htm由于旋轉件不平衡量離心力的影響,在轉動時,中心慣性主軸與回轉軸線不重合,所以慣性力矩或慣性力偶矩的大小與方向會隨著機械運動的循環而產生周期性變化,從而使得整個機械系統產生振動。由于振動對機械設備的工作精度、壽命等有很大影響,甚至可能損壞設備,所以大部分的旋轉件需要做動平衡。

多數的動平衡測量系統的工作環境比較惡劣,周圍存在很多其他設備,電磁和機械干擾可能同時存在,所以對測量系統的抗干擾性等要求更高。所以對現有測試系統的改造勢在必行。提高系統集成度,減小系統復雜度,提高系統運算能力將有效解決上述問題。在此基礎上我們采用了基于SOC技術的C8051F單片機作為系統核心。由于速度快,功能豐富,可以實現A/D轉換、數字采集、操作控制、LCD模塊顯示、輸出數據、與上位機通訊和高速運算等功能。

1 測試系統構成

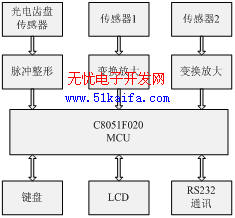

系統一般要采集兩種信號,由光電齒盤產生脈沖信號,經過脈沖整形,用來測量被測件的轉速與相位,并由此決定A/D采樣的時機;由壓電傳感器產生的壓力信號(一般為兩路),用來測量振動幅值。兩個壓電傳感器的信號經過壓電變換、放大和硬件濾波后,由A/D進行采集。轉換后的數字信號由MCU進行計算,解算出振動的幅值和相位,然后通過LCD顯示。系統主要功能模塊如圖1所示。

圖1 測試系統框圖

2 系統硬件設計

MCU采用C8051F020處理器,這是完全集成的混合信號系統級芯片,它既能接收模擬信號又能接受數字信號,其采用CIP-51TM微處理器內核,與8051完全兼容,并且在速度上有顯著的提高。完全的工業級設計,抗干擾能力強。芯片內部集成了64KB的FLASH程序存儲器,比較器模塊,SPI和I2C接口等。片內JTAG調試電路允許使用安裝在最終應用系統上的產品MCU進行非侵入式、全速、在系統調試。內部集成12位分辨率的逐次逼近寄存器型ADC,ADC 中集成了跟蹤保持電路,速度高,轉換速度可達100ksps,完全滿足測量精度與速度需要。

2.1 A/D轉換電路設計

該A/D轉換采用C8051F020內部集成的12位A/D轉換器,只需配置好參考電壓和時鐘信號源即可。由于有8路外路模擬通道,在接外部模擬信號時,應將外部模擬信號相鄰通道接地,以免電源毛刺、地電平波動以及交互串擾等影響轉換結果。

2.2 顯示器與鍵盤設計

由于C8051F020有著豐富的I/O,可用I/O口數量多達64個,并且中斷資源豐富。所以鍵盤和顯示器的連接不用擴展I/O口。鍵盤采用矩陣式鍵盤,并選擇中斷方式。因為LCD的顯示內容不實特別多,速度要求不是特別快,所以為方便起見,LCD的控制采用模擬時序的控制方式,僅需要14個I/O口就可以實現并行方式。

3 系統軟件設計

動平衡測試系統在實際使用中會遇到各種干擾,包括電氣干擾和機械振動干擾。電氣干擾一般有工頻干擾和尖峰脈沖干擾,機械干擾則包含了各種雜散振動干擾,所以傳感器的輸出不僅有不平衡量引起的基頻振動信號,還含有各種頻率成分的干擾信號,所以我們需要采用一定的算法消除干擾信號,提取有用信號。由于C8051F的速度較傳統的8051速度快很多,其運算能力提升了近十倍,所以我們可以在不影響顯示速度的前提下,采用更復雜、精度更高的算法。

3.1 DFT與FFT算法

FFT算法精度比較高,雖然在速度上較相關分析等算法稍微慢一些,但是由于單片機的速度提升了很多,所以不會影響測量與顯示的速度。

由傅立葉分析可知,一個周期信號可以分解為許多不同頻率正弦信號之和,即可以將周期信號看成是各次諧波之和。采集到的信號是離散的數字信號,所以需要采用離散傅立葉變換(DFT),進行頻譜分析。

設有效采樣點序列為:f(0),f(1),f(2)…f(N-1),N為一周采樣點數,離散化后的傅立葉變換為:

只需要提取基頻分量就可以得到被測件的不平衡量。相位依上述公式算出。

即快速傅立葉變換(FFT),實利用DFT變換的特性,優化運算方法,大大降低了運算的時間復雜度,點數越多,速度提升越明顯。所以為了提高運算速度,實際的運算程序采用優化的FFT算法。

評論