IC業在拐點生存

拐點挑戰之三:IC成本和ESL

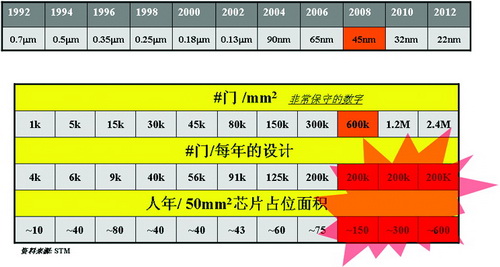

本文引用地址:http://www.j9360.com/article/86940.htm“在今后幾年中,我們所要面臨的大多數問題可以歸類為各種成本核算問題。”Mentor Graphics公司Design-to-Silicon部總經理Joe Sawiki指出,其中包括實現芯片工廠的成本;開發新技術節點的成本;設計芯片的成本等等。這些將推動電子業的創新。例如,在過去幾年中,設計成本和與之相對應的技術節點所帶來的附加固定資本(real-estate)幾乎持平。也就是說,開發一個65nm產品或一個獨立芯片會花費3千萬美元,再加上其它常規功能,這意謂你需要一個具有5倍開發成本(1.5億美元)商機的市場來銷售這個芯片。這就是為什么一些設計正在走下坡路的原因。如果展望一下在未來的幾年中,32nm 和22nm在硅芯片固定資本方面會呈現的局面,你會看到設計領域將發生翻天覆地的變化(圖2)。實現一項特定設計所花費的成本將會出奇地高。

圖2 設計業發生翻天覆地的變化

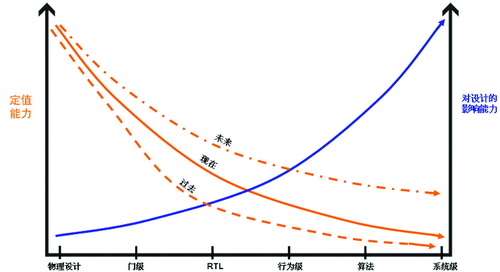

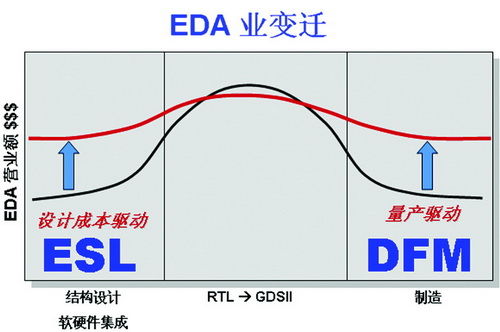

Mentor Graphics公司CEO兼董事會主席Walden C.Rhines指出,當設計成本高達5~6千萬美元時,因制造環節的問題而導致芯片失敗是完全不能被接受的(圖3)。在系統設計方面,ESL已被談論很久了,遠比DFM久(圖4),DFM只有三、四年的時間。阻止設計方案實施的原因是設計的復雜性增加了。人們都說產品的生命周期正在逐漸縮短。

圖3 通過改進系統架構,來改善功耗和成本

圖4 EDA的變革

功耗已經被多次討論過了,不過如何強調這個問題都不算過分。對于系統的功耗問題,最終建議采用ESL在一個新的抽象層設計出解決方案。但這需要對所采用的工具進行重大技術改革。

Walden C. Rhines

Mentor Graphics CEO兼董事會主席

ESL需要具備的條件

擁有一個完整的ESL系統需要具備以下幾個條件(圖5):

圖5 理想的ESL流程

首先,在高端需要有一個處于執行層面的建模環境,它可以讓你把時序、功耗、功能和界面接口等的結果(effects)分開。在這個建模環境下的工作效率比所有RTL建模環境的快幾百倍。它讓你在更高的層面使用你的設計,讓你決定控制的類型、數據流的形式以及軟件的形式。你可以進行結構性的決策,它們會對功耗產生多種多樣的影響。這些是在較低層面進行設計時做不到的。

其次,你需要能對各項描述進行綜合。如果你不得不把設計從高一級層面手工轉化到下一級層面的話,在這種環境下,只需導入一個全新的驗證層面就可以了。

還有,并不是所有設計都是全新的,許多設計在實現階段采用了大量已有的設計單元,有些是舊有的設計,有些則是來自第三方IP提供商;這些設計中有些帶有TLM(事務級模型),一些則沒有,因為這些設計在被導入之前都已被實現了。所以你要能把舊有的設計從RTL中抽取出來放入TLM環境中,將所有的設計單元合為一個完整系統。

最后,假如在使用C/C++的測試系統中實現含有RTL的設計,你則需要一個多語言環境來完成它。

到目前為止,限制ESL應用的諸多因素之一是這項技術的許多部分事實上還不存在,或是仍處在初期階段。但Mentor預期在未來的幾年中,這項技術將進入設計領域并會顯著地降低設計成本。

評論