基于FPGA電火花加工脈沖電源的設計

2.2軟件編程實現

本文引用地址:http://www.j9360.com/article/85842.htm軟件編程采用Altera提供的軟件編譯環境NIOS II IDE。Nios II IDE基于開放和可擴展的Eclipse平臺,不僅可以將通用用戶界面和業界最好的開發環境完美結合,還能夠與第三方工具無縫地集成在一起。Nios II IDE提供了完整的C/C++軟件開發套件,包括編輯器、項目管理器和構建工具、調試器和兼容CFI(common flash interface)的Flash編程器。Altera提供含有支持Micrium的MicroC/OS-II實時操作系統(RTOS)。該系統不用用戶修改任何代碼即可進行系統移植。使Nios II開發者能很容易地在Nios II IDE中實現多任務軟件開發。

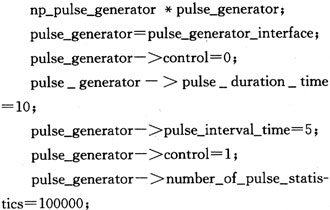

軟件的開發過程是在IDE中創建一個工程文件,工程所指定的硬件系統即是在Quartus中生成的.ptf文件。新的工程將包括2個庫,一個是用戶的API庫,另一個是系統庫,系統的庫中包含了用戶進行軟件編程時需要的各種頭文件、驅動程序等。在用戶庫中可以使用C/++或者是匯編語言編寫脈沖參數的實現功能,在寫好后就可以對軟件工程進行編譯、調試得到希望的結果后就可以軟件的工程文件.elf下載到開發器件上。如果需要調整脈沖、脈間的參數,則可以在NIOS IDE中對脈寬與脈間的比例以及周期長度進行修改。同時通過對I/O口輸出的高低電平,可以控制每一路大功率管的關斷與否,從而做到了電流大小的控制,具有非常高的靈活性。這樣可以得到新的適合進行粗、中精、精加工的脈沖序列。用戶程序中對脈沖控制及參數控制的代碼如下:

2.3系統仿真

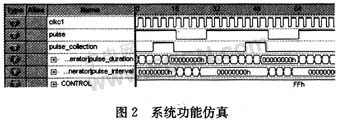

我們可以用Quartus對設計的系統的功能進行仿真,以驗證功能是否滿足要求。軟件文件下載到開發板后對電路進行仿真的結果,如圖2所示。從圖中可以看到脈寬pulse_duration_time與脈間pulse_interval_time的比例參數,以及控制寄存器的值,同時還可以看到該系統的輸入時鐘的周期長度,放電脈沖的周期長度等信息。

3外部電路設計

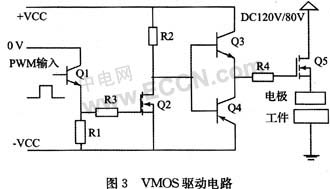

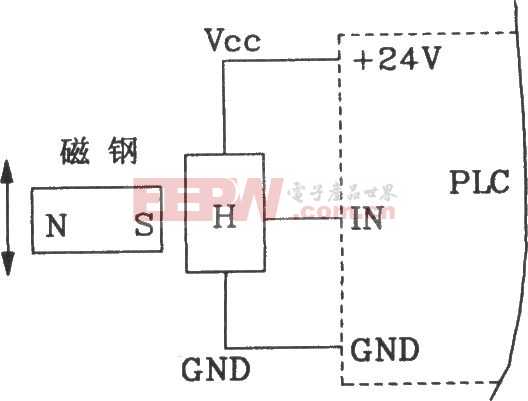

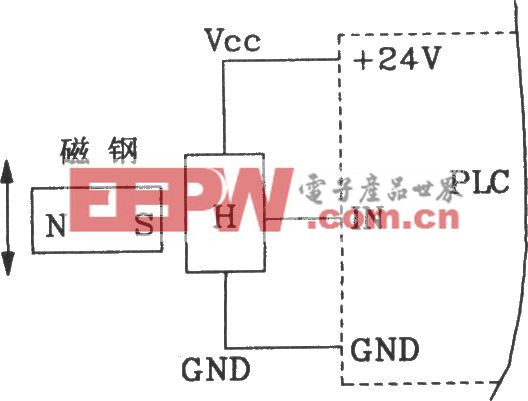

外部電路主要包括直流電源、隔離放大電路、高速開關電路、保護電路。直流電源電路是市電經過變壓器、整流橋路電路、電容濾波電路輸出的,輸出的電壓有+80 V和120 V兩種,分別用于粗加工和精加工。脈沖發生器的PWM用來控制高頻開關管,為了防止脈沖發生器的燒壞,要將FPGA開發板與開關管電路隔離開來,而電源的頻率很高,普通光耦的會產生波形畸變,所以采用的是25M的高速光耦PC412S。開關管采用的是VMOS,使用它的好處是開關的頻率高,能夠承受的電流和電壓都比較大,但要使用輸入電容較小的VMOS,否則會影響電源關斷的速度。開關管的驅動電電路如圖3所示。

Q1的基極是從FPGA開發板經過光耦輸出的PWM脈沖信號,通過后面的驅動電路來驅動Q5,從而實現放電加工電路中采用正負電源,這樣可以提高Q5的關斷速度。Q2是小功率的VMOS管,Q3和Q是用來驅動大功率的VMOS,所以功率不能選太小,R3與R4是用來減小系統波形的振蕩,其阻值不能太大,可選取100 Ω。

4結 論

本文在EDM機理與嵌入式技術領域最新研究成果的基礎上,針對目前微細EDM加工中電源的研究現狀,提出了一種新型的智能型EDM脈沖電源,該電源的脈間精度可以達到0.2μs,是一般的分立軟件和集成電路所不能達到的,脈寬,脈間的大小可參數話,這些設置都是在軟件中進行,并且采用FPGA設計具有可進行更新,保密性好。這種新型的脈沖電源,由于高電火花脈沖放電頻率,從而提高加工精度。又因為HDL語言和FPGA技術的應用越來越廣泛,所以這種智能的脈沖電源具有很好的通用性。

linux操作系統文章專題:linux操作系統詳解(linux不再難懂)

評論