基于CPLD的USB下載電纜設計

引 言

本文引用地址:http://www.j9360.com/article/82548.htm隨著片上系統(SoC,System on Chip)時代的到來,包括復雜可編程邏輯器件(CPLD,Complex ProgrammableLogic Devi(e)和現場可編程門陣列(FPGA,Field Programmable Gate Array)的可編程邏輯器件(具有在系統可再編程的獨特優點),應用越來越廣泛。這給用于可編程邏輯器件編程的下載電纜提出了更高的要求。

本文研究基于IEEEll49.1標準的USB下載接口電路的設計及實現。針對Altera公司的FPGA器件Cy-ckone,通過分析它的邊界掃描測試結構和各種JTAG指令,研究它的編程過程和編程特點,并提出設計方案。在接口電路硬件設計中,選用FTDI公司的USB控制芯片FT2蠣BM,實現USB物理層和鏈路層協議的解析;Altera公司的可編程邏輯器件EPM7064實現接口邏輯。與傳統的基于PC并口的下載電纜相比,本設計的USB下載接口電路具有支持熱插拔、體積小、便于攜帶、降低對PC硬件傷害、編程速度快等明顯優點。

目前已開發的USB下載線一般需要在主機端另行設計軟件來控制與下載線及目標器件之間的通信和數據傳送;但是這樣不僅繁瑣,而且可能由于PC機操作系統的不同而影響兼容性。本文討論的USB下載線能在A1tera公司的QuartusII開發環境下直接使用,無須在主機端另行設計通信軟件。

1 系統結構及工作原理

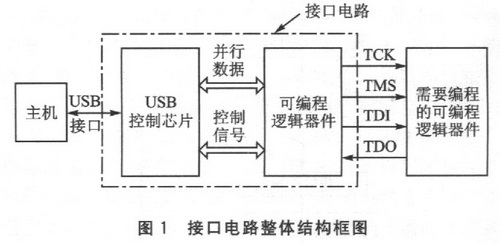

接口電路的整體結構框圖如圖l所示。由于USB下載電路涉及了IEEEll49.1標準和USB協議,所以接口電路主要包含兩大部分。一部分是USB接口,它連接主機和可編程邏輯器件,主要功能是進行USB和并行I/O口之間的數據格式轉換,用USB控制芯片實現。另一部分是JTAG接口,它連接USB控制芯片和需要編程的邏輯器件,主要功能是進行并行I/O口和JTAG之間數據的轉換,轉換邏輯通過對可編程邏輯器件進行設計來實現。其他還包括一些必要的時鐘電路和電壓轉換電路。

從主機傳來的USB數據,由USB控制芯片轉換為8位并行數據,經數據總線送到CPLD的可編程I/O引腳。CPLD的數據也可以通過數據總線送回USB控制芯片,然后轉換為USB的數據格式傳回主機。CPLD收到USB控制芯片傳送來的數據后,對數據進行解析,然后轉換為符合IEEEll49.1標準的編程數據和指令,從TCK、TMS和TDI串行輸出到要編程的可編程邏輯器件。從可編程邏輯器件返回的符合IEEEll49.1標準的校驗數據從TDO串行輸入到CPLD,轉換為8位并行數據傳送給USB控制芯片,最后返回主機進行校驗。

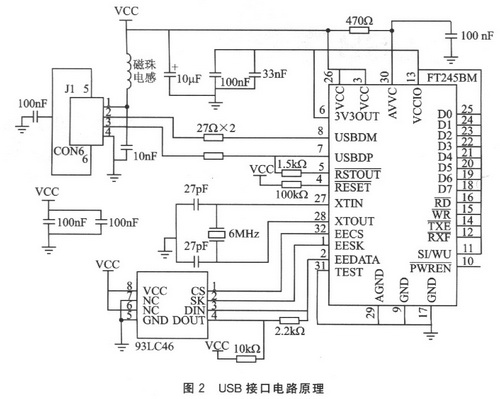

USB控制芯片FT245BM負責解釋USB協議,完成雙方數據通信。其內部有USB協議引擎,并且集成的電平轉換器使FIFO和控制信號能與電壓為5 V、3.3 V的邏輯器件接口。USB接口電路原理如圖2所示。

2 對目標器件的配置過程

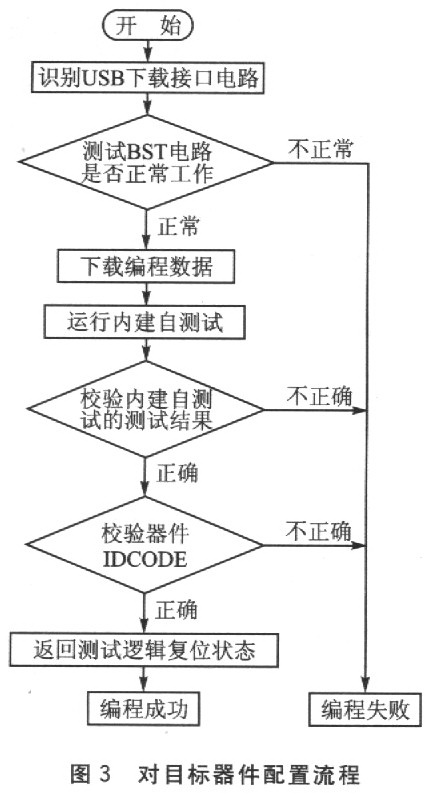

對目標器件的配置流程如圖3所示。

(1)識別USB下載接口

Quanus II編程器通過PC的USB接口向FT245BM依次發7e、7f、7c三個數據。FT245BM經PC的USB接口向編程器依次返回3個數據03。在編程器收到返回的3個03以后,編程器就識別此USB下載接口電路為它的下載硬件平臺。

(2)測試BST電路

測試包括以下幾個方面:

復位測試;

指令寄存器移位測試;

標志寄存器移位測試。

(3)下載編程數據

這個步驟把所有的編程數據從PC下載進可編程邏輯器件的配置存儲器。因為這一步驟下載的編程數據龐大,所以下載時采用特快模式,并且不進行校驗,避免影響下載速度。下載選用的指令是Ahcra公司自己定義的DOWNLOAD指令(00 0000 0010)。

(4)內建自測試

內建自測試是在電路內部建立測試生成、施加、分析和測試控制結構,使得電路能夠測試自己。

(5)校驗器件的IDCODE

在整個編程流程結束以前,再一次校驗器件的ID—CODE,確認器件的BST電路在下載編程數據后足否工作正常。這一步的過程和標志寄存器移位測試完全相同。

(6)返回測試邏輯復位狀態

保持TMS為高6個TCK周期,使TAP控制器進入測試邏輯復位狀態,并且讓TMS保持為高電平,以保持測試邏輯復位狀態。這樣器件的測試邏輯失效,器件的核心邏輯開始正常工作。

結語

本文所討論的USB數據下載線能在Altera公司的QuartusII開發環境下直接使用,無須另行開發主機端通信程序。與傳統并幾的編程方式相比,優勢十分明顯:支持熱插拔,使用更方便;體積更小,攜帶方便;編程速度更快,節約時間。為國際數字系統設計領域內正蓬勃興起的在線編程(ISP)技術的推廣與發展提供了有力的支持。

評論