邊界掃描測試技術(04-100)

—— 邊界掃描測試技術

最近出現的系統級接口器件,為設計人員把用于制造測試的邊界掃描測試從板級擴展到系統級提供了靈活條件。

本文引用地址:http://www.j9360.com/article/81044.htm擴展到系統級的基礎結構是提供單點接入到多掃描鏈,以支持隔離的診斷能力。這可以用于CPLD和FPGA系統內配置的最佳化,以及編程閃存時存儲器讀/寫周期的最佳化。

它也支持板到板內連測試(用于背投內連失效診斷)到端口連接器引腳級。另一個優點是在產品裝運前提供系統測試,這包括固件檢驗和簡化固件更新。

擴展邊界掃描到系統級提供執行嵌入式測試結構(即器件級BIST)的基礎結構,這可在EPGA、ASIC和SoC中實現。

另外,它提供單點接入能力來支持環境重點測試和精確的引腳級診斷。

拓撲結構

選擇邊界掃描系統結構對于路由TAP測試接入端口是重要的,并將確定選擇哪些系統級器件。有三種主要的TAP路由方式:ring(環狀)star(星狀)multi-drop(多分接)

當然,多分接方式是最廣泛用于可靠系統控制的。在這種方式中,5個主要的IEEE1149.1測試接入信號(TCK,TMS,TDI,TDD,TEST)并聯連接到系統配置的所有背板槽中。

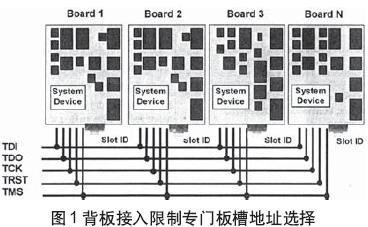

多分接配置中的每個槽都有一個專門的地址,槽地址多達64/128個專門地址,通常,這些地址在背板中用硬線連接(見圖1)

通過總體掃描鏈的TDI信號線,廣播每個板的專門背板地址來接入系統中的每塊板。對應于廣播地址的置于槽中的板,將喚醒并允許接入到本地掃描鏈,這如同用系統器件接入協議進行選擇哪樣。

linux操作系統文章專題:linux操作系統詳解(linux不再難懂)

評論