靈活的動態電源管理解決方案

嵌入式系統產品的主要差別是其電源效率,因為較低的功率導致低運作成本、低扇出噪聲和低冷卻要求。因此,現代嵌入式系統著重于增強系統功能,同時降低運行功耗、增高工作頻率,或者采用更強大、更高密度的VLSI集成電路以提高系統的性能,但是又不可避免地增加了功耗。減少系統級功耗的一種方法是使用低靜態功耗的器件。此外,在系統運行期間的功耗主要取決于所處理的負載。這種方法稱為動態電源管理。

本文引用地址:http://www.j9360.com/article/78390.htm基于CMOS技術的數字系統中,下面的數學方程描述了功耗、工作頻率和電壓之間的關系。

系統功耗= aC×V2×F

方程中C是信號傳輸時所有電路中需要充電的總電容。V是加至器件的電壓,F是信號切換頻率。從方程中可知,降低電壓或頻率,或者同時降低兩者,能夠降低整個系統的功耗,這是動態功率管理的基本原理。動態功率管理鑒別低處理要求時段,降低工作電壓和頻率,這樣就能減少平均運作功耗。此外,在空閑時段,關閉電路板上某些電路的電源可以進一步減少功耗。

系統運行期間,由軟件來決定電壓或者頻率的減少量。本文闡述了作為這一電源管理軟件的外設工作的電路。

動態電源管理方法的幾個問題

設計一個具有動態電源管理能力的系統時,設計者應該認識到下列問題:

1.工作電壓與頻率的執行時間。

電源需要一定的時間上升到新的工作電壓,這個延時通常是電源總線上負載的函數。對于時鐘發生器來說,頻率之間變化所要求的時間可以是很短暫的。因此,操作系統必須監控工作電壓以及決定什么時候改變頻率。

2. 電壓或頻率的轉變期間處理器或許不能可靠工作。

電源電壓或輸入時鐘頻率改變時,許多能夠工作在不同的電壓和相應頻率的CPU也許不能可靠地工作。在這種情況下,建議在電壓或頻率的轉變時,暫停CPU的工作。這就要求外部的硬件電路監控電壓和頻率,阻止CPU在轉變期繼續工作。

3. CPU與集成的PLL通常產生集成的外圍設備產生所需要的頻率,也為外部總線接口提供時鐘。倘若CPU時鐘頻率改變,PLL必須重新編程以維持外圍設備的工作頻率,這些外圍設備并未設計成工作于不同的頻率。含有片內PLL的CPU會使頻率范圍受到限制。一個外部的PLL能容易地克服這個限制,擴展節約功率的范圍同時又能滿足電路板上使用的其它外圍設備的時鐘要求。

動態電源管理實現的原理

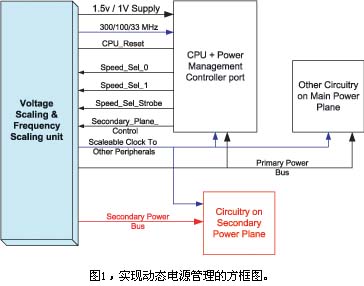

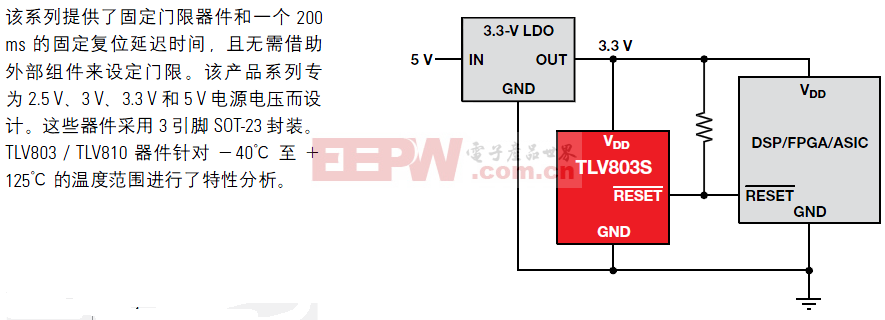

電路板上實現功率管理功能的框圖如圖1所示。用軟件來實現電源管理算法,用硬件來定標電壓和頻率,以此共同控制整個電路板的功耗。

1.控制CPU和電路板上其它電路的工作頻率;

2. 控制CPU的內部電壓;

3. 空閑期間關閉第二組電源;

在圖1的左面,電壓標定和頻率標定單元接受來自電源管理端口的命令并產生要求的內部電壓、CPU時鐘頻率以及關閉或開啟第二組電源總線。電源管理信號如下:

Speed_Sel_0 Speed_Sel_1 命令信號譯碼為

00 全功率 CPU電壓=1.5V,工作頻率=300MHz

01 中等功率 CPU電壓=1.0V,工作頻率=100MHz

10 低功率 CPU電壓=1.0V,工作頻率=30MHz

11 用這個信號控制第二組電源 0 關閉第二組電源;1開啟第二組電源

Speed_Sel_Strobe 鎖存來自電源管理控制器端口的命令,電路板上其余的電路分為主電源電路和第二組電源電路。

萊迪思公司的ispPAC Power Manager 和 ispClock5520能非常方便地實現寬范圍的動態電源管理功能。

ispClock5500特性

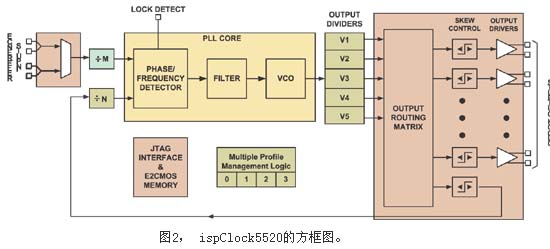

ispClock5500系列有兩個器件,10個輸出的ispClock5510和20個輸出的ispClock5520。它們可以構成靈活的高性能時鐘產生器,具有通用扇出緩沖器。時鐘產生器能提供多達5個時鐘頻率,從10MHz到320MHz,采用高性能的PLL和時鐘倍頻,分頻功能。通用扇出緩沖器能驅動使用單端或者差分的20個時鐘網絡,且有獨立的用于改進信號與時序完整性的輸出控制功能。這些新器件有著優越的性能和靈活性,支持電路板上的高性能時鐘網絡設計。

可編程 I/O:輸入部分為兩個硬件可選的多路時鐘輸入。輸出部分為多達20個低扭曲時鐘輸出。參考時鐘輸入和時鐘輸出可以分別編程,然后與單端邏輯(LVTTL LVCMOS SSTL HSTL)和差分邏輯(LVDS LVPECL Differential HSTL Differential SSTL)相接口。輸入和輸出終端電阻可編程范圍在40Ω~70Ω,以每5Ω為一檔。每個時鐘輸出的輸出扭曲可以獨立地設置成16檔中的一種,分辨率為195ps。扭曲的間隔大小源自PLL頻率,因此是非常精確的。頻率綜合單元能夠產生多達5個時鐘頻率。無阻塞的輸出轉換陣列可以把任意頻率送至任意輸出。輸入頻率范圍從10MHz到320MHz,輸出頻率從5MHz到320MHz。

PLL核:器件的核心是高性能PLL核,由相位頻率檢測器(PFD),可編程片上濾波器和VCO組成。PLL核能鎖存的輸入頻率范圍是10MHz到320MHz,而輸出頻率范圍在320至640MHz,輸出抖動小于100ps。

頻率綜合分頻器:器件有7個5位計數器:M,N和5個V計數器。M,N和一個V計數器有5位分辨率用于設置PLL的工作頻率。PLL的輸出驅動其余的V分頻器,只與PLL工作頻率相關的5個獨立頻率得到了綜合。

JTAG編程和掃描接口:器件使用JTAG接口編程,也可以用標準的在線檢測器檢測電路板的互聯關系。

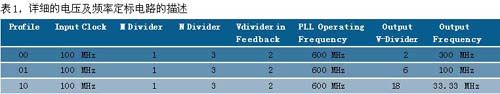

時鐘管理模式:器件能存儲4個獨立的配置(M、N、V計數器和扭曲),能選擇4組獨立的時鐘頻率。電路的頻率定標使用了ispClock的管理模式特性,為CPU提供3個時鐘頻率,300MHz、100MHz和33MHz。其余的輸出可以通過編程提供3個時鐘頻率的4組,使用其余的V計數器,這些時鐘與CPU的時鐘不同,所有的功能均通過相同的選擇引腳來控制。此外,設計使用ispClock的同步選通信號(Sync_gate),用以防止畸形的時鐘周期。下列表格列出了不同的管理模式對應的各種配置值。

設計實例:Power

1208p1+ispclock5520方案

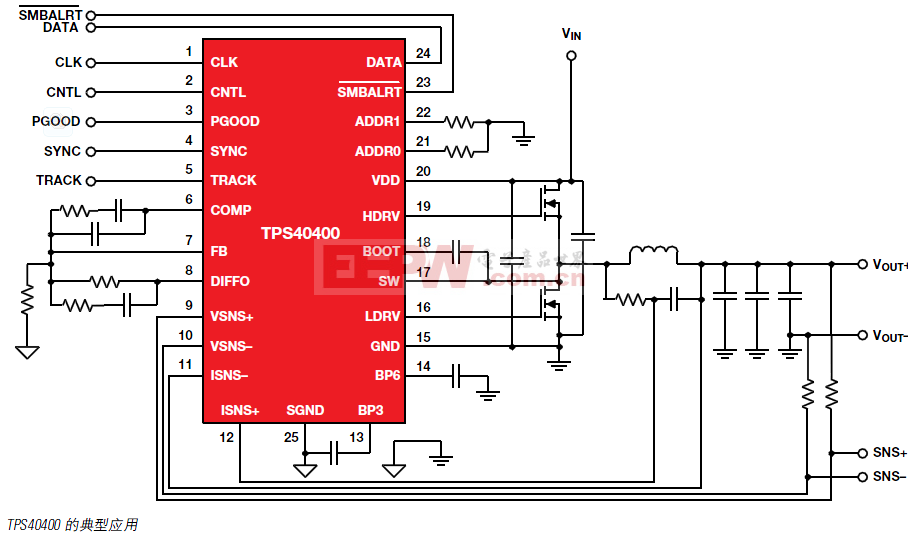

圖3為Power1208P1(ispPAC-POWR1208P1),器件提供所有的邏輯功能,用于電壓和頻率的定標功能。此外還驅動ispClock5520。考慮到電壓和頻率的轉變時間,它遵循來自電源管理端口的命令,獨立地控制第二組電源。ispClock5520產生所要求頻率定標的各種時鐘頻率。總共有20個時鐘輸出,通過編程產生用于電路板各部分的不同時鐘頻率。

Power1208P1的功能包括:寄存與執行來自電源管理控制端口的命令;控制B1電壓在1.0V和1.5V之間變換;監控所有電源電壓;產生用于ispClock至輸出頻率之間轉換的控制信號;開啟跟蹤主電源總線;控制跟蹤第二組電源總線;上電時脈沖展寬CPU復位信號,電源發生故障時激活CPU復位信號。

ispClock的4種模式中的3種可以配置產生不同的時鐘頻率,這里只討論CPU頻率的改變,同樣的機理可用于所有時鐘輸出。

電源B1的電路運作:通過調整引腳和輸出電壓引腳之間連接電阻R1和R2,圖3中頂部左面的電源B1的輸出電壓可設置成1.5V。如果只把R1連接在輸出和調整輸入之間,輸出電壓為1.0V。MOSFET Q1開啟時,將電阻R2短路。結果B1的輸出電壓變為1.0V。然而,Q1關閉時,B1的輸出電壓成為1.5V。驅動MOSFET Q1,控制HVOUT引腳斜率,在電壓從1.0V變至1.5V或者從1.5V變至1.0V時,限制電流涌入。

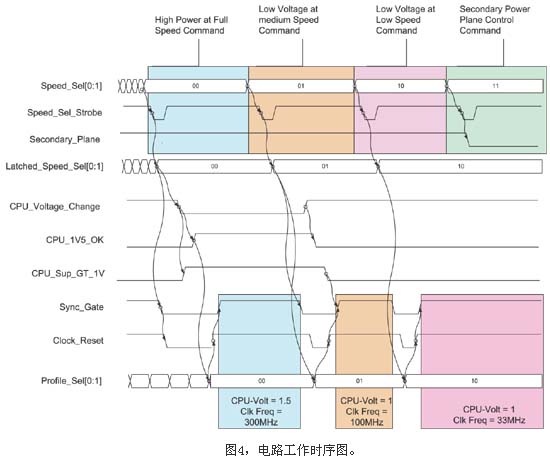

圖4為上述電路工作的時序圖。圖的頂端是來自電源管理控制端口的命令。Power1208P1和ispClock5520執行命令。電源電壓和時鐘頻率到達穩態后,這個穩態是穩定的。

上述設計在最小的電路板面積上提供了最大的靈活性。IspClock5520對時鐘頻率定標功能是理想的,因為它可以取代4個獨立的時鐘產生器件和與之相關的從多路時鐘緩沖器中選出一路時鐘的價格昂貴的邏輯電路。

用于這個設計的Power1208P1器件不但有電源電壓還有監控邏輯信號的能力。此器件的邏輯部分能在控制電源電壓和監控CPU電壓軌跡的同時,方便地集成所有的邏輯功能,能可靠地在不同的工作速度之間進行轉換。其結果是設計能夠在配置之間安全地轉換。

電源濾波器相關文章:電源濾波器原理

負離子發生器相關文章:負離子發生器原理 分頻器相關文章:分頻器原理 塵埃粒子計數器相關文章:塵埃粒子計數器原理

評論