13.2A 50mW的帶通SD ADC(模數轉換器)

圖1對

圖2

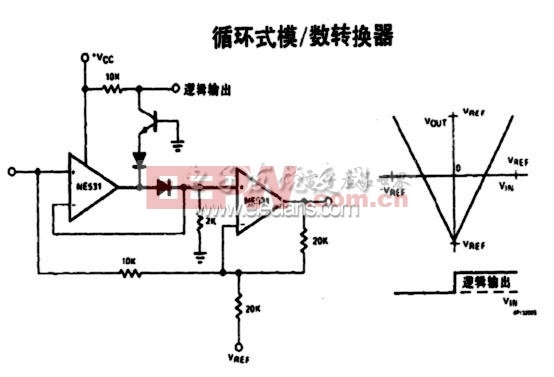

圖1對將一個中頻信號進行數字化的兩種方法進行對比。第一種方法需要幾種大功率的模塊,即,可變增益放大器(VGA),抗混疊濾波器(AAF)和ADC,而第二種方法將此模塊用一個帶LC諧振電路的帶通SD ADC所替代。借助時間連續環路濾波器,帶通SD ADC對固有混疊進行保護,省去了AAF。由于ADC的輸入噪聲較低,且它的電流型輸入能提供較強的信號,所以它的動態范圍較寬,因此,

圖2是較詳細的ADC結構。鑒于上述討論,低噪放(LNA)加混頻器的跨導視為gm=10mA/V。低噪放加混頻器的輸出電流2mApp直接作為ADC的輸入,而沒有經過不必要的I-V或V-I轉換。8個元件的電流型DAC(IDAC)的電流減去反饋數字輸出電流,生成一個驅動LC諧振電路的誤差電流。LC諧振電路由兩個外部5.6mH的電感和一個電容組成。通過一個9位片上電容陣列將電容值微調到所需值的1%以內。LC諧振電路在相關頻帶內的有效阻抗為Z=6KW,此阻抗將造成12VPP的電壓擺動,如果不是來自于IDAC的反饋,IDAC的反饋只能導致以下的電壓擺動。前端電路較大的有效增益為gmZ=60,當低噪放有輸入信號時,會使ADC后端的噪聲由減少到只有。由于此噪聲比低噪放/混頻器的輸入噪聲低8dB,因此,ADC的后端對IC噪聲特性的影響不大。由于LC諧振電路不產生噪聲,加之無失真和不耗電,因此,LC諧振電路是帶通SD ADC中理想的第一諧振器。

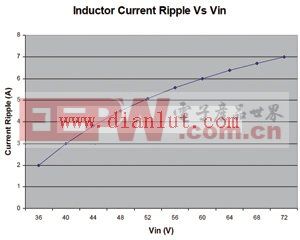

圖3

VGA通常用于當信號較弱時,通過增益來降低ADC的輸入噪聲。但是,圖2中的VGA是ADC的一個內部元件,它的主要目的是當信號較弱時降低功率消耗。為了平衡大信號的電流,IDAC元件的總電流必須為2mA,但是當信號較弱時,元件的電流可以降低(本方案中降低了1/4),以節省功耗。全面地改變IADC可以相應地改變ADC,使AGC功能得以實現。全面地降低IDAC可以減小ADC后端的信號擺動,并且利用圖中的可變增益元件使電路得到最有效的補償。為了保持調制器的動態范圍,VGA的增益會隨IDAC的全面波動而反向變動。VGA作為一個其gm值可變的模塊,通過改變非退化雙極結型晶體管(BJT)差分對中的拖尾電流來控制。

ADC的第二個諧振器也使用了一個LC諧振電路。圖3中的VGA和有源RC諧振器消耗2mA的電流,并且不需外部元件就能滿足第二級動態范圍的要求。可編程電容陣列可以實現RC諧振器的調諧。

評論