iLink技術測試和驗證高速總線

摘 要:本文介紹了一種新的高速總線測試和驗證方法,通過ilink工具包、集成邏輯分析儀和數字存儲示波器,能夠幫助設計和測試人員徹底的調試、驗證各種高速串行和并行總線。并且通過多路通道的眼圖測試可徹底驗證高速信號完整性問題。最后給出了高速總線測試和驗證的實例。

關鍵詞:iLink工具包;iConnect;iView;iVerify;信號反射

引言

對于計算機普遍采用的并行總線來說,隨著系統時鐘和數據速率的提高,多位并行總線變的很難同步。對于每一個并行信號,由于高速會帶來噪聲和通道間的串擾,CPU必須等待所有的總線全部穩定,以保證它們能夠被很好的鎖存下來。并且在每一個時鐘的有效沿處,數據和時鐘的定時關系必須滿足建立/保持時間,數據才會被穩定的存儲下來。這些并行總線的限制使之很難達到單一信號傳輸超過1GHz。同時,為了滿足更高的帶寬要求,目前計算機和通信領域越來越多采用簡單架構的串行總線。現在的一個16位或32位的并行總線可能變成為1位或2位的串行總線結構,并且具有更高的數據傳輸率。無論是復雜的高速并行總線還是串行總線都向設計和調試人員提出了新的挑戰。因為當時鐘頻率達到數百兆或更高時,每個設計細節都很重要,需要認真考慮電路中的時鐘分布、信號路徑、殘樁引線、噪聲容限、阻抗和負載、傳輸線影響以及功率分配等問題。所有這些方面都會對高速通信系統中傳輸的數字信號完整性產生影響。

高速總線中的信號完整性問題

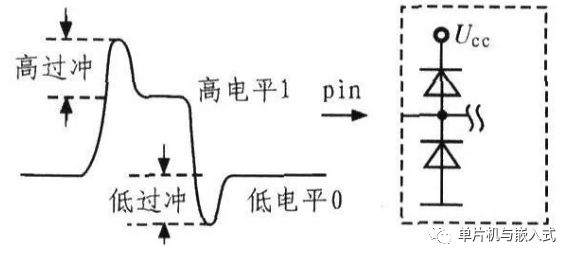

在高速總線中,典型的信號完整性問題包括以下幾部分:振幅問題:包括減幅振蕩(震鈴效應)、“下垂”脈沖(在脈沖開始處的下降振幅)和“欠幅”脈沖(不能達到正常振幅);邊沿畸變:包括預過沖、過沖回擺、過沖、震鈴效應和緩慢的上升時間。邊沿畸變可能產生于高速電路板布局問題,或是半導體器件的質量問題;信號反射:向外發出的信號會朝信號源頭方向彈回,并干擾隨后的脈沖。造成反射的原因有可能是端接和電路板布局問題;接地跳動:在電流需求大時可造成電路接地參考電平的偏移。接地跳動由過流、電源或接地回路阻抗引起;串擾效應:當在電路板上出現并行的長引線時,其信號可通過電容和電感的相互感應而耦合,從而產生串擾。另外,快速邊沿中較高的電流可增加輻射電磁能,并隨之產生串擾;定時抖動:當數字信號在周期間包含有微小的邊沿位置變動時,就會產生抖動。這種抖動將影響整個數位系統的定時準確性和同步。

定時問題引起信號完整性故障

數字信號畸變產生于許多根本性原因。在并行總線中,與定時有關的問題是非常普遍的現象。

總線競爭

當兩個驅動器設備試圖同時使用同一總線時,就產生了總線競爭現象,它會導致信號畸變。正常情況下,當一個驅動器傳送數據時,另一個驅動器應進入高阻抗狀態并保持“讓路”狀態。但如果高阻抗的設備不能及時切換,就會出現兩個驅動器爭用總線的情況。由于兩個驅動器信號都不能通過,故迫使總線形成一個不確定的振幅,這樣就可能達不到邏輯電路的閾值電壓。

建立/保持時間違規

帶鎖存功能的數字器件要求時鐘和輸入數據必須滿足建立/保持時間的要求。否則會在輸出數據上出現不可預見的毛刺,或根本沒有正確輸出跳變(稱為亞穩態效應)。高速同步總線中,對建立和保持時間的要求特別嚴格,僅分析定時關系很難進行故障排除。

iLink工具包進行高速總線驗證和調試

高帶寬數字存儲示波器是信號完整性分析的傳統工具。它可用于捕獲被測數字信號的模擬參數信息,并且能方便準確的顯示方波、瞬時尖峰脈沖,以及各種各樣的信號完整性問題。邏輯分析儀是計算機和通信系統硬件調試的有力工具,特別是對那些擁有大量總線、輸入和輸出裝置的高速系統。它具有高通道數、深存儲器和先進的觸發功能,可從許多測試點捕獲數字信息。而且現代邏輯分析儀都包括能夠幫助檢測某些對信號完整性有影響的觸發功能。例如毛刺觸發、建立和保持時間違規觸發等等,這些觸發條件,以及許多其他邏輯組合觸發條件可同時應用于數百個通道上。為了加速高速計算機和通信系統的總線調試和驗證,泰克公司提供的iLink工具包,將TDS示波器和TLA715系列邏輯分析儀集成在一起,共由iConnect,iView,iVerify三個部分組成。

iConnect技術

隨著各種高速總線出現,以及產品的空間尺寸要求越來越小,如何進行信號的探測和連接是每個設計人員都必須面臨的問題。傳統的高帶寬示波器通過探頭的附件來連接被測信號、觀測數字信號的模擬參數細節、進行調試和驗證。邏輯分析儀由于需要連接更多的通道,例如觀察32位地址總線、數據總線以及關鍵的時鐘和控制信號,需要幾十路,甚至上百路信號同時觀測。所以在設計階段,進行可測性設計就顯得至關重要,需要專門提供足夠的測試點保證邏輯探頭探測高速總線。為了保證高速信號的探測和連接,在TLA7AXX系列邏輯分析儀模塊中采用的P6860探頭(34個通道),前端采用有源鍺化硅電路,每一個探頭的輸入容性負載為0.7pF,并且提供2GHz的模擬帶寬。

在連接方式上,P6860探頭和被測電路的連接采用壓接的方式,即無需傳統的、為邏輯分析儀探頭測試提供的測試插座或連接器。探頭的前端為高密度導電膠條,工程師在進行可測性設計時,只需要按照探頭指南所提供的機械尺寸,在PCB板上設計部分測試焊盤即可。這種無連接器方式的邏輯探頭連接可以保證PCB布線測試點時產生的殘樁盡可能的小,并且減小了進行可測性設計時的布線復雜度。

采用iConnect技術的有源邏輯探頭,能夠直接在測試過程中通過示波器配合來直接對數字信號的模擬參數信息進行觀測,無需再使用示波器的探頭在被測電路板上尋找測試點來重復探測。圖1中顯示了一套邏輯探頭完成信號測試的方法以及TLA7AAX系列邏輯分析儀的內部結構。有源邏輯探頭分成4組,每一組34個測試通道,送入到邏輯分析儀中去。然后經過一組2GHz帶寬的模擬多路開關(它可以任意切換136個通道中的4個通道作為模擬輸出),送入到任意一臺外部TDS示波器中去,這樣示波器就可以對設計人員在邏輯分析儀中選擇的4路通道進行模擬參數信息的觀測。同時,136個通道的信號送入邏輯分析儀中,經過8GHz的采樣保持電路,實現邏輯分析儀的功能。并同時進行8GHz的高速定時分析、2GHz的通用定時分析、800MHz的狀態分析。此外,由于TLA715邏輯分析儀中提供iConnect功能,所以可以直接根據設計人員的選擇從136路信號中選擇4路送入到示波器中。

iView技術

傳統的技術并不能進行信號完整性問題的全面分析。數字示波器能夠捕獲數字信號的模擬參數,分析故障的細節信息,但是受到通道數和觸發能力的限制,并且它是物理層的分析工具,無法從整個系統的角度去發現故障。邏輯分析儀可以從數據層上觀測一個錯誤數據,例如可以發現一個通信系統的十六位地址錯誤,但卻無法分析錯誤產生的根本原因。如果能夠深入觀測信號行為并看到有缺陷數字信號的模擬特性,那么查明許多數據錯誤就會簡單很多。iView技術集成了兩種信號完整性分析工具的特點,將數字示波器(須滿足被測系統模擬帶寬的需要)連接到邏輯分析儀(須有適當的通道數量、存儲深度和采樣率),通過將模擬域和數據域的工具聯合起來,觀測模擬參數信息的同時可以觀察相同信號的數字碼流信息,從而設計人員就可以察覺并排除系統中的錯誤。

iView技術進行故障調試實例

假設在時鐘為120M的高速總線傳輸中出現數據錯誤,通過邏輯分析儀的毛刺觸發功對整個總線上的所有通道進行故障查找。發現在數據線D3的第3位上有邏輯毛刺出現,造成數據傳輸錯誤。為了分析D3(3)總線上出現邏輯毛刺的原因,聯合數字示波器觀測邏輯毛刺的模擬細節。圖2中是邏輯分析儀和數字存儲示波器時間相關的觀測波形結果,模擬信號捕獲結果出現在邏輯分析儀屏幕的中心,顯示了毛刺的本質。邏輯分析儀的定時采樣率為8GS/s,示波器的采樣率為20GS/s,在數據總線D3(3)的模擬信號上升沿和下降沿處有明顯的單調性問題。通過集成分析技術,發現毛刺是由于信號反射造成的。經檢查發現在電路板上D3(3)引線上有殘樁,導致高速信號的反射效應,通過電路板重新布線解決了這個故障。

iVerify技術通過眼圖測試對總線徹底驗證

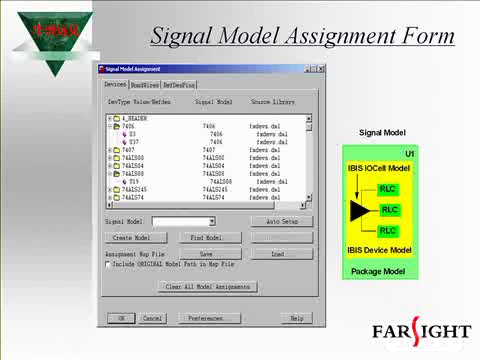

在高速總線測試和驗證時,眼圖是信號完整性測試的重要方法。實時示波器和采樣示波器是眼圖測試的基本工具。示波器由于受到測試通道數目的限制(4個通道),有時候還需要一個通道作為外部時鐘進行同步。在多路高速總線中,為了徹底驗證系統,需要對所有總線信號進行眼圖測試。iVerify技術建立在iConnect技術和iView技術的基礎上,它能夠一次對408路總線進行眼圖測試來徹底驗證被測信號。結合iConnect技術,使用一套邏輯分析儀有源探頭進行信號邏輯和模擬的同時觀測,邏輯分析儀可以將被測通道分成多組,每一組3個數據通道送入到示波器中進行眼圖測試,示波器的第4個通道作為外部時鐘。采用iView 技術,邏輯分析儀可以自動的將每一次送入示波器的3個數據信號的眼圖測試數據傳到邏輯分析儀中,這樣邏輯分析儀就可以再選擇另外一組3個通道進行測試。對于復雜的高速總線,可以一次測試408個數據通道。最后,iVerify技術通過邏輯分析儀將408個數據信號的眼圖測試數據疊加顯示出來,徹底驗證總線中出現的信號完整性問題。圖3是iVerify技術的實現過程。

iVerify技術進行總線驗證實例

假設在時鐘為120M的高速總線傳輸中,有2組總線A2(7)~A2(0)和A3(3)-A3(0),共12個通道數據。首先采用iConnect技術,通過一套2GHZ帶寬的邏輯分析儀探頭P6860完成對總線信號的探測。然后通過邏輯分析儀的iVerify功能來一次分析12個通道的眼圖,并在邏輯分析儀上通過色溫的方式疊加顯示出來。TDS7704B(7GHZ帶寬)測試的眼圖數據被自動的傳送到邏輯分析儀中。在邏輯分析儀中提供了6種自動測試功能:4邊形自定義模板、6邊形自定義模板、眼高眼寬測量、上/下極限模板、信號斜率測量、水平直方圖統計,以及垂直直方圖統計。可以進行12路總線的測試。觀察A2和A3兩組總線眼圖,并進行4邊形模板測試結果,經過測試發現在A2(0)的總線上有830個樣點進入到模板的禁止區域。

結語

信號完整性問題是高速數字系統硬件設計的關鍵,設計人員不僅需要發現信號完整性問題,還要分析問題出現的原因,徹底驗證高速總線。通過邏輯分析儀和數字存儲示波器的iLink工具包,結合了兩種不同分析工具的優點,彌補了傳統分析方法的不足。利用邏輯分析儀的iConnect簡化對被測系統的探測和連接,配合高帶寬示波器,可以對多路高速總線進行徹底的驗證。■

參考文獻

1 Howard Johnson Martin Graham. High-speed digital design: a handbook of black magic. Prentice Hall. 1993

2 John F.Wakerly . Digital Design Principles&Practices (Third Edition) . 高等教育出版社. 2001

3 Tektronix,Inc .Tektronix Logic Analyzer Family Version 4.3 Software User manual. 2003

評論