CS434x系列DAC及其應用

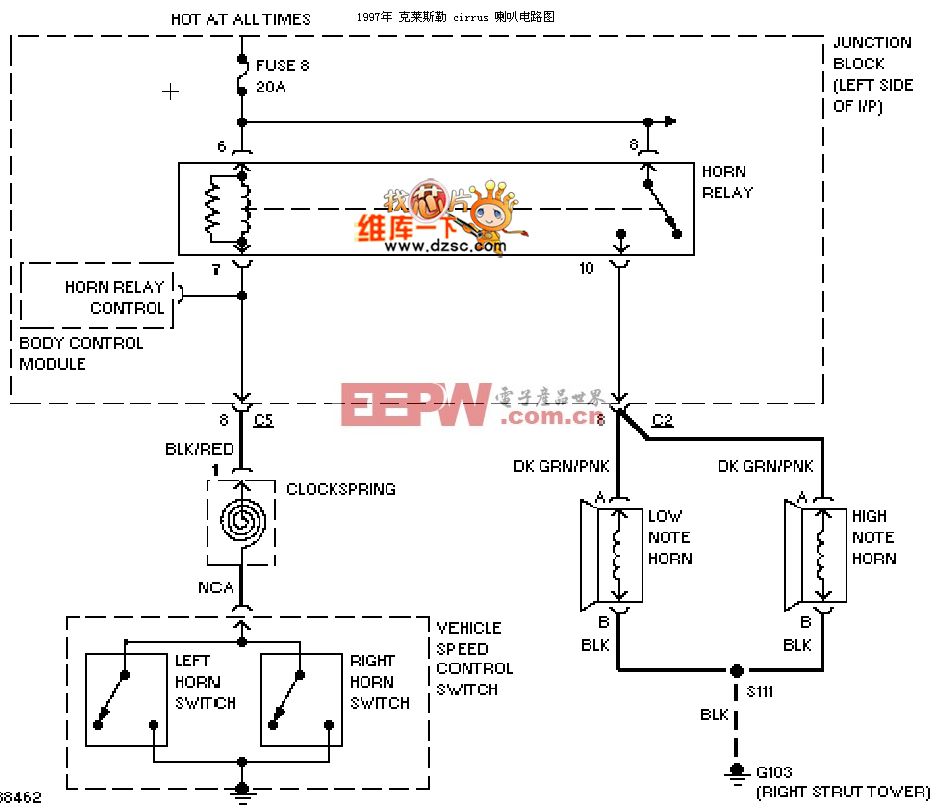

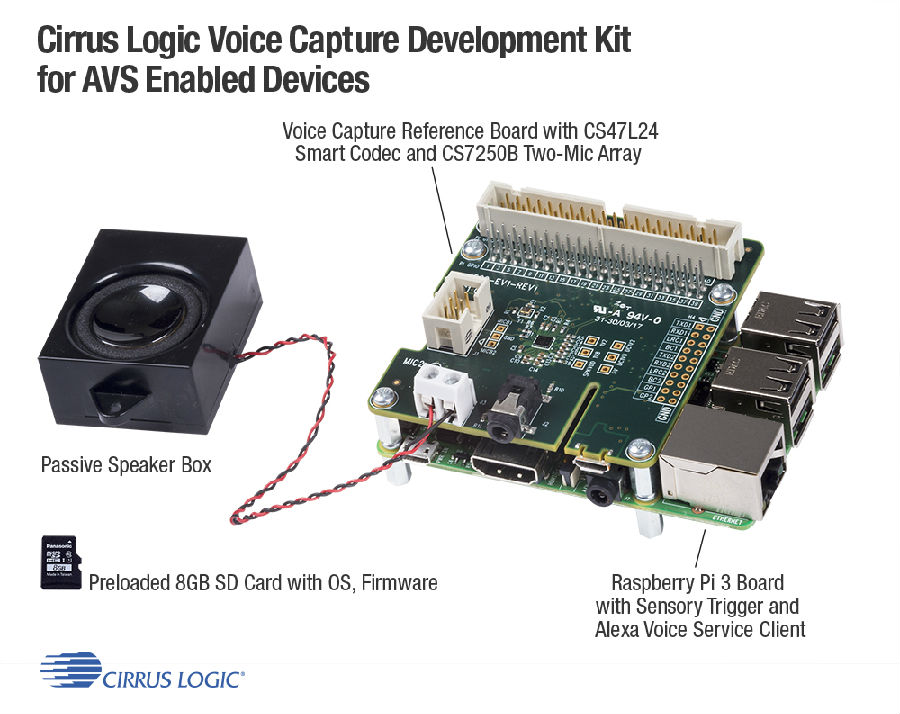

CS434x 系列基于先進的多位 Delta-Sigma 結構,提供單端輸出,總諧波失真加噪聲為 -95 dB,動態范圍達 105 dB。CS434x 系列可在 +3.3 V 或 +5 V 單電源下運行,并具有其它高附加值性能,如:擁有專利的自動采樣率檢測、片上數字去加重,以及能夠消除電源循環嘀嗒聲和爆破聲的Popguard技術,有助于減少外部器件的數量。內部結構如圖1所示。

CS4344、CS4345、CS4346 和 CS4348 之間的區別僅在于它們所支持的串行音頻接口格式,分別包括 I2S、左調整以及 24 位和 16 位右調整。由于該系列與CS4334、CS4340 和 CS4340A等廣泛使用的產品兼容,因此已經采用這些產品的廠商只需簡單升級即可獲得最新功能。

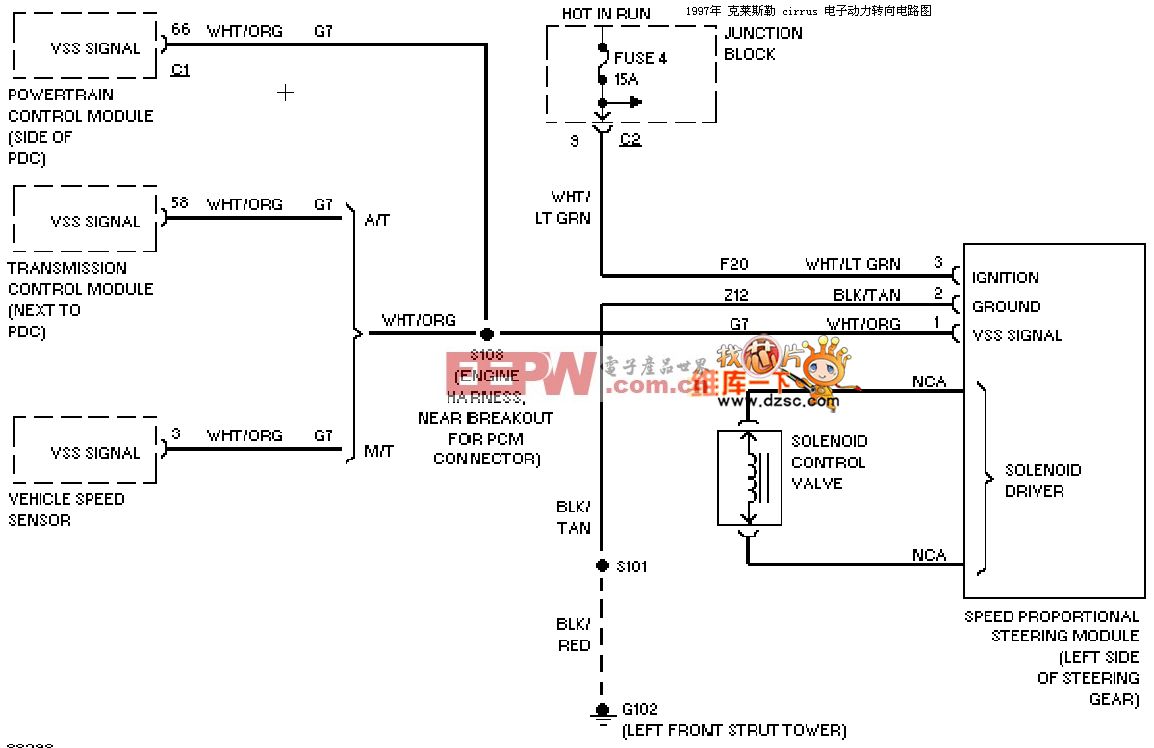

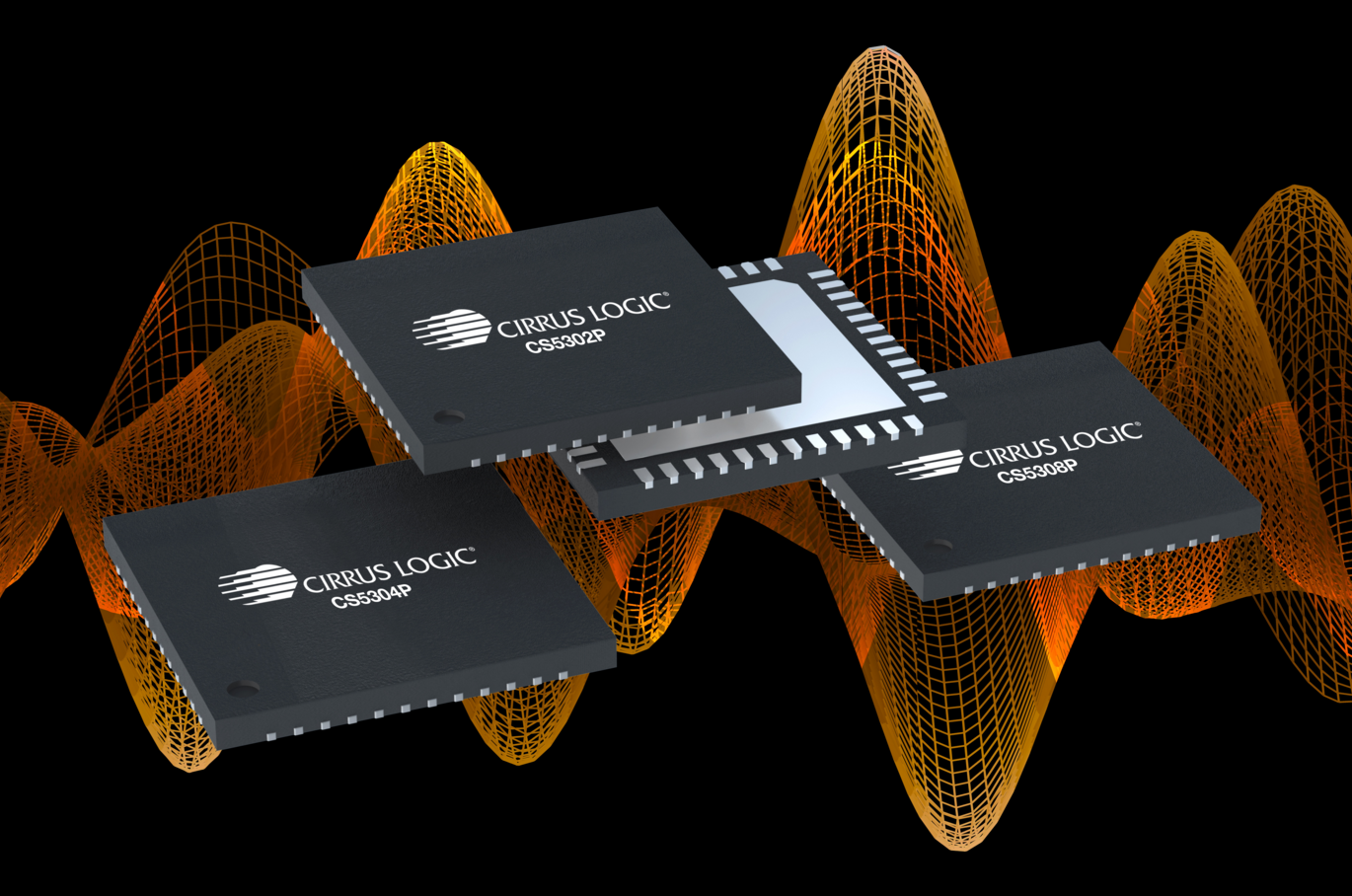

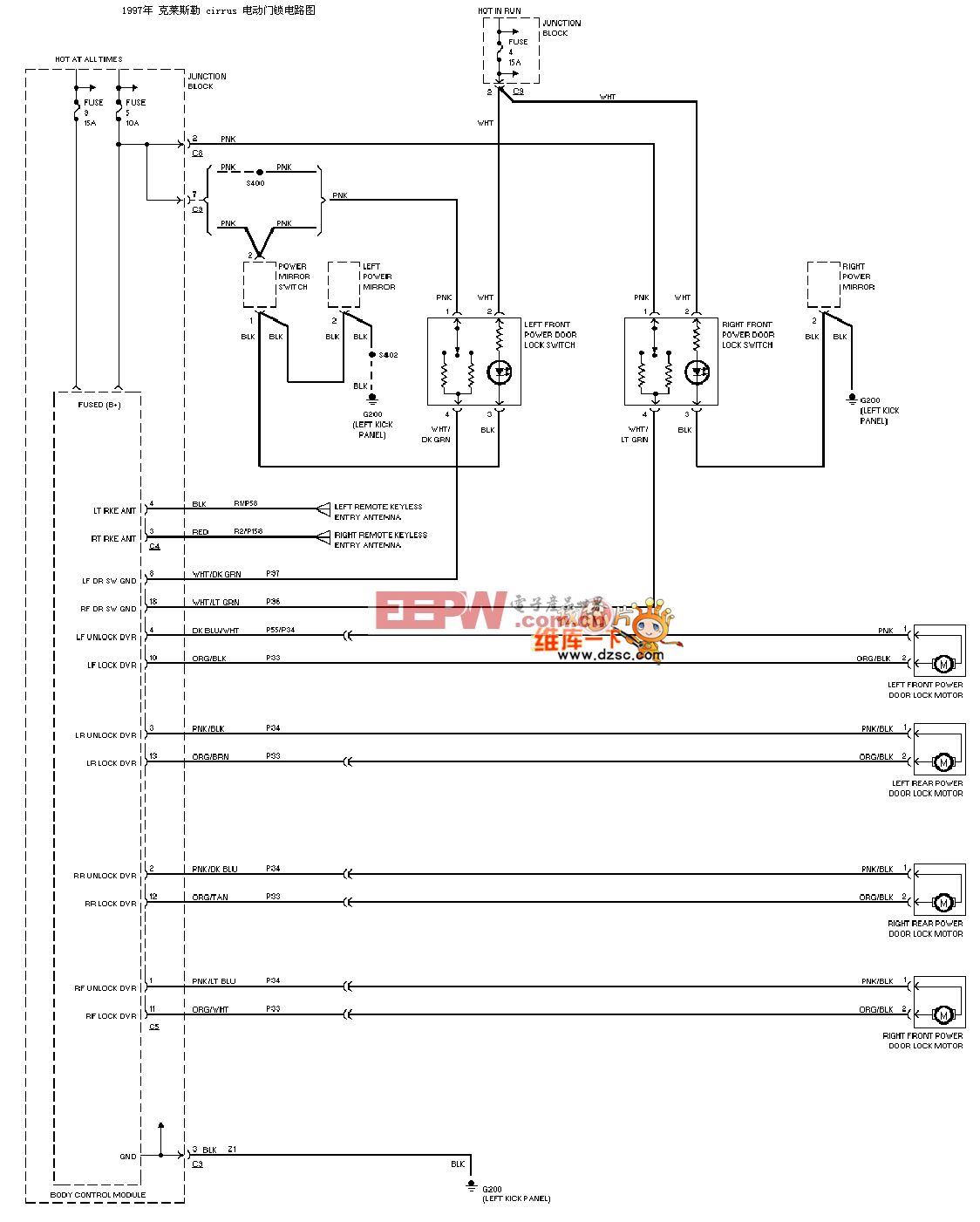

CS434x 系列允許以48、 44.1 和 32 kHz (SSM),96、88.2 和64 kHz (DSM),192、176.4和 128 kHz (QSM)等標準音頻采樣率接收數據。音頻數據通過串行數據輸入引腳(SDIN)輸入。左/右時鐘(LRCK)決定目前哪個通道通過SDIN輸入數據,而可選串行時鐘(SCLK)則對進入數據緩沖器的音頻數據提供時鐘。CS4344、CS4345、CS4346 和 CS4348 在串行數據格式方面的差別如圖2~5 所示。

MCLK/LRCK 必須為整數,如表 1 所示。LRCK 頻率等于 Fs,即每個通道向設備輸入數據的速率。通過計算單一周期內 MCLK 轉換次數及檢測 MCLK 的絕對速度,可以在初始化系列期間自動檢測到 MCLK 與 LRCK 的比值和速度模式。內部分頻器自動生成合適的時鐘。表 1 解釋了幾種標準音頻采樣率以及所需 MCLK 和 LRCK 頻率。應該注意,盡管對相位關系無要求,MCLK、LRCK 和 SCLK 卻必須是同步的。CS434x 系列同時支持內部和外部串行時鐘生成模式。

在 LRCK 周期的任何一個階段,當監測到 DEM/SCLK 引腳上發生 16 個從低到高的轉換時,CS434x 系列就會進入外部串行時鐘模式。如果該模式被激發,則無法進入內部串行時鐘模式和去加重過濾器。如果在 LRCK 的兩個連續時段監測不到 DEM/SCLK 引腳上從低到高的轉換,則 CS434x 系列將轉入內部串行時鐘模式。

在內部串行時鐘模式中,串行時鐘由內部生成,并與 MCLK 和 LRCK 同步。SCLK/LRCK 的數值根據數據格式不同,有32、48、64、72 四種。在該模式下運行和在與 LRCK 同步的外部串行時鐘模式下運行是一致的。該模式可獲得數字去加重功能。■

分頻器相關文章:分頻器原理

評論