縱觀3G基站開發的變化

基站接口規范

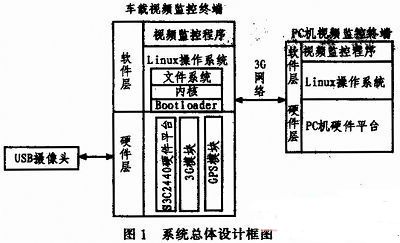

在如何進行3G基站開發方面,2004年被證明是具有顯著變化的一年。通用公共無線接口組織(CPRI)和開放式基站結構同盟(OBSAI)分別提出了兩個標準,用來規范基站內開放的、標準化的接口。兩個組織已經公布了它們的技術規范,支持新標準的產品也開始出現。圖1為OBSAI標準定義的開放接口實例。

圖1 OBSAI 標準定義的開放接口實例

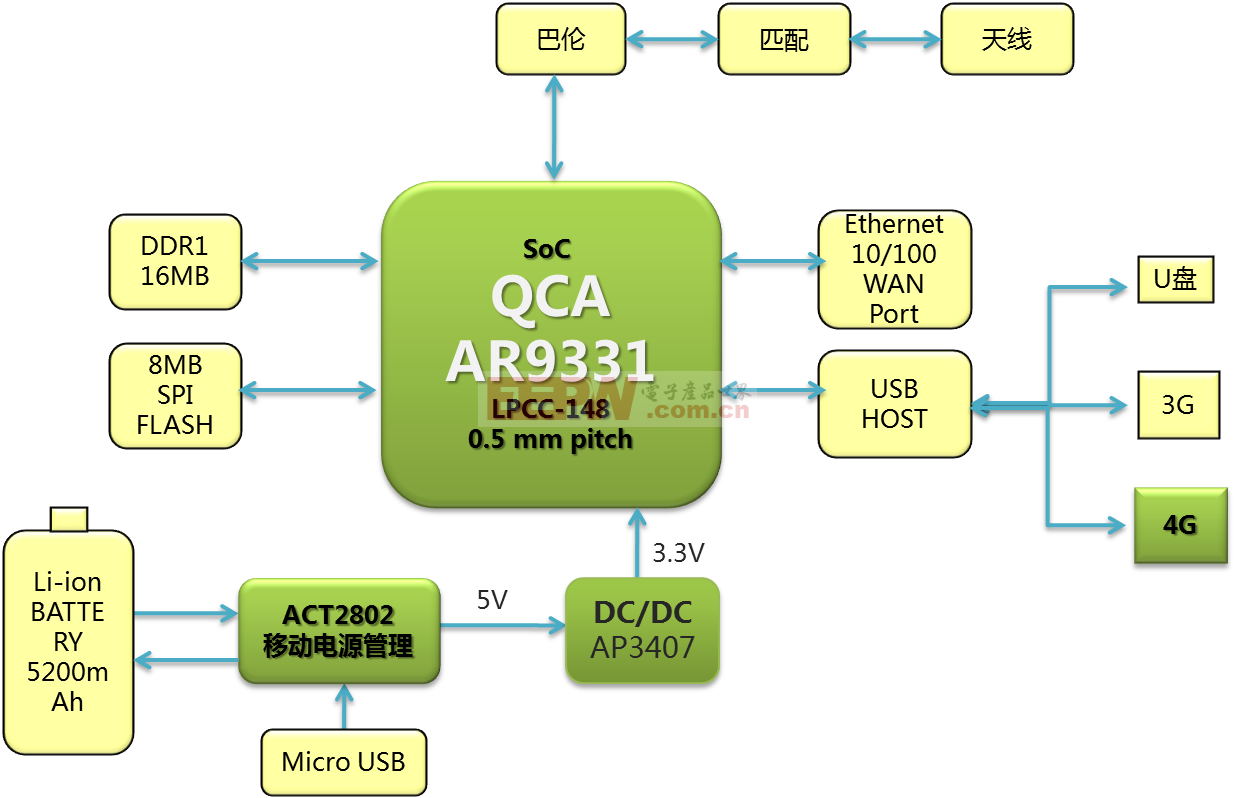

圖2 針對寬帶功率放大器線性化的基本數字預失真系統

兩個標準由不同的無線基礎設施提供商獨立發起。諾基亞、三星、LG和中興通信支持OBSAI標準,西門子、愛立信、北方電信、NEC和華為支持CPRI標準。但是兩者都重點關注基帶信號處理和射頻子系統之間的接口,并作為標準化的關鍵領域。而且兩個新標準的目標是相同的,即通過創建針對基站模塊開發的有競爭力的市場,減少開發成本和產品成本。但是這些新的標準將影響對3G基站內DSP功能的開發。對于理解這些標準將如何影響傳統射頻產品和DSP的集成,基站內嵌模塊—射頻功率放大器是關鍵。

射頻功率放大器

對于基站射頻功率放大器,如果不是來源于無線通信設施提供商內部,通常是由Powerwave、Andrew和Remec等公司開發,對于這類產品必須剪裁接口以適應網絡基礎設施提供商的專用技術規范。

在工業領域,通用標準是減少成本的一種手段,而對于一個通用的數字接口,包括CPRI和OBSAI提供的,將促使供應鏈發生變化,即“誰需要知道什么”。這主要是由于數字線性化和效率助推功能,比如波形整形和數字預失真(Digital Pre-Distortion)功能將成為一體化射頻子系統的關鍵部分。

在過去的十年里,由于寬帶射頻功率放大器的功率效率能夠從2~4%提高到20%,帶來很大的系統成本的節省。因此數字預失真技術已經成為很多大型無線基礎設施公司重要的研發投入,圖2為針對寬帶功率放大器線性化的基本數字預失真系統。但是由于新的接口被設計到內部,數字預失真處理將不得不轉移到射頻子系統提供商和正在尋求提供針對射頻子系統的完整芯片集解決方案的芯片提供商。

目前,針對數字預失真的硅片ASSP解決方案已經在市場上出現,它們來自PMC Sierra 公司和Intersil公司。但大的通信基礎設施公司的開發者仍然在調整他們的技術,因此不太情愿采用外部解決方案。調整數字預失真算法通常需要大量的調試且非常復雜—這似乎對FPGA制造商有好處(例如Xilinx 和Altera),因為作為首選的硅片解決方案,也許FPGA天生就已經被確定作為在大批量產品中主要DSP功能的補充技術。圖3是Xilinx特定應用的模塊化ASMBL FPGA解決方案。

圖3 最新的來自Xilinx特定應用的模塊化 ASMBL FPGA解決方案

基帶處理方案

在3G基站內DSP功能的主要領域當然是WCDMA基帶處理。盡管在這個領域的主要驅動力來自正在成長的硅片解決方案,它使得一直充滿前景的軟件無線電成為現實。但是新的數字接口的另一端是射頻子系統,所以這里也存在“誰需要知道什么”,在供應鏈中同樣是變化的。新的3GPP特征,例如高速下行分組訪問(HSDPA)、“智能天線”和多輸入多輸出(MIMO)天線陣列正在收集更大的增益,具有縮短開發時間和現場升級能力的基于軟件的基帶實現方法,正在變成每一個通信設備提供商產品策略的重要方面。

在過去的幾個月里,很多重要產品的發布已經表明:基帶處理的基于軟件的設計解決方案正準備在專用的ASIC上實現,這使得產品成本更具有競爭力,并縮短了設計周期。這些主要的發布包括:

ADI公司的TigerSHARC TS201采用全速“Danube”架構,具有強大的解擴和相關性指令。后者對于UMTS有效的進行隨機接入(RACH)前導碼檢測和多路徑搜索非常重要。

Motorola公司的MRC6011可重配置計算結構,具有24G次乘法累加操作計算能力以及針對擴散和相關性的專用指令,采用Morpho公司的MS1可重配置DSP陣列處理器構建而成。

PicoChip的PC102是一個陣列處理結構,能夠執行38G MAC,并且對于相關性操作可達到140G CMAC。

TI公司的720MHz TCI100 DSP: 對于64信道 UMTS基帶處理,適宜采用TI的包括該DSP的3片解決方案(其它兩個器件是TCI110發送器ASSP和TCI120接收器ASSP)。

Intrinsity的2.5GHz FastMATH自適應信號處理器,提供了靈活的ASIC/FPGA性能,而且通過采用易于編程的內嵌處理器,加快了產品的上市時間。

在以上諸多解決方案中,TI的解決方案以帶有ASSP器件的強大的DSP為核心,實現了芯片級的運算速度(嚴格上講,不是一個真正的“全軟件”方案)。

ADI已經進行了向全軟件解決方案的轉換,使用強有力的單處理器架構,通過獨特指令集完成傳統硬件才能實現的芯片級處理功能。

Motorola使用有趣的并行陣列處理架構實現芯片級處理功能,并通過一個多重的StarCore DSP MSC8126進行符號級速率的處理。

PicoChip 已經開發了一種大塊并行架構,通過使用3個不同種類的、高度優化的處理器實現所有芯片級速率處理、符號級速率處理和控制操作功能。

目前已經有產品在使用高度并行的處理結構,可以預測,在實際的3G產品中,并行處理器結構方案將能夠戰勝規模不斷升級的“傳統DSP架構”。

在高速并行、可重配置架構方面,FPGA最終可能變成另外一個重要的競爭者,因為90nm/300mm產品技術降低了成本,增加了密度——這種把“硬”和“軟”處理器技術與傳統的FPGA“硬件”相結合所形成的能力,為應對基帶處理設計的挑戰提供了一種強有力的工具包。

在這些方法中,決定性的因素不是他們的最終產品成本的降低,而是通過提供庫,甚至完全的硬件和軟件解決方案,帶來產品成本和開發費用的共同降低。很多大的無線基礎設施公司正在從傳統的硬件方法向現在的、具有成本效益的軟件解決方案轉移,從而具有更多的靈活性和對市場需求的響應能力。但是在這個轉變過程中,很多公司正指望通過庫的使用減少他們的開發成本,并且集中他們的資源重點關注基帶領域,在這里能夠看到與傳統領域的真正差異—這些傳統領域包括信道評估和頻率偏移校正算法以及在呼叫建立和呼叫控制過程中的功率控制和微調。

目前為止,只有picoChip公司已經發布了完全的、一致性測試的“軟件參考設計”方法,但是很明顯,其它的參與者包括FPGA提供商都正在朝這個方向邁進。可以預見,一些新涌現的DSP提供商將提供“標準”WCDMA基帶解決方案,并能被3G產品提供商所采用。

一些大的產品公司正在研究針對基帶功能的API,從而展開了基帶硅片提供商之間的競爭,但這不會對更高層NodeB軟件造成影響。這種接口可能會集成到新出現的基站框架標準中,使得基帶DSP成為基站內另外一個“標準化”的功能模塊。

隨著開放基站的快速發展,針對DSP芯片提供商和集成商的機遇和挑戰都是巨大的。這方面的很多問題都正在被進行深入探討。 (于永學譯) ■

評論