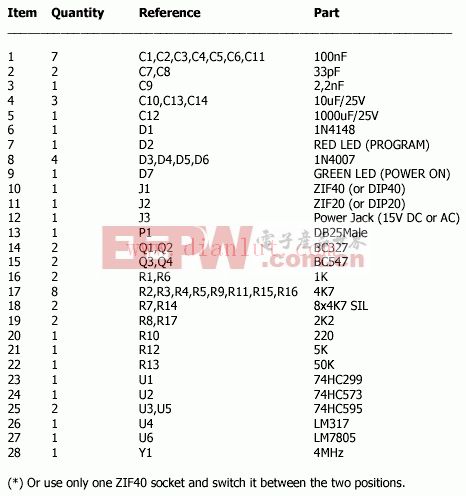

系統級集成軟件顯著縮短產品面市時間

工程師已經在實驗室里工作了兩個多星期,可是你的板子還是不工作,看看硬件,再修改一下軟件, 配置器看起來完全沒問題,到底是哪里出了問題呢?當然這一次的項目比上一次的更加艱難,不僅軟件程序加大,FPGA更加復雜化了。當終于找到問題所在時,項目又要再一次的面臨漫長的延遲了, 除非有一個SoC,一個可以把軟件和硬件同時設計好并可以在幾小時之內就可完成修改的SoC,就是因為這個理由使工程師在一開始時就選擇可編程的邏輯單元。

FPSLIC縮短開發周期

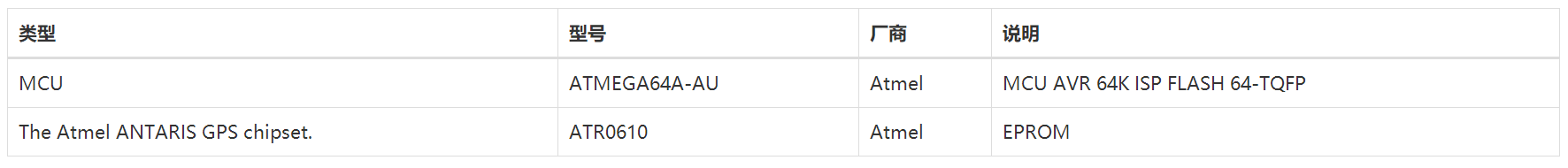

目前很多公司推出的SoC基于很大的FPGA,但Atmel找到了一個更有效的途徑來解決此問題。在最新推出的FPSLIC (Field Programmable System Level IC)里有五千到四萬門以SRAM為主的FPGA、326000bits的程序和數據SRAM、一個25M的快速8位AVR單片機,和幾個不同的但很受歡迎的外圍設備。此構想的主要原因是為了提供一個既方便又好用的SoC。它不僅可以縮短產品上市時間,更可以降低成本,減少設計上一些不必要的麻煩。

圖1 系統設計軟件-FPGA、單片機和同步仿真軟件

全部都在一個窗口里

圖2 同步仿真顯著的減少產品面市時間

系統級集成軟件提升FPSLIC性能

很多設計問題不單純是簡單的硬件或軟件的問題,真正的問題所在往往是在把它們整合在一起的時候才會被發現。當運行單片機指令、診斷硬件和器件接觸時可發現大部分的問題在硬件和軟件的接觸界面上,只有專門的軟件才可以減少漫長的硬件開發和系統級集成的時間。Atmel提供的系統設計軟件如圖1所示。

同步仿真

Atmel系統設計軟件的同步仿真結合軟件和硬件提供設計者已熟悉的開發環境。同步仿真不僅可以提前把軟件集成,這可以給FPSLIC設計帶來以下幫助:

?使軟件開發和硬件開發同時進行;

?降低重復修板的次數;

?提前發現和修正硬件和軟件的接口問題;

?給設計者時間去探索其他在硬件和軟件上的分配;

?減少物理實現后在實驗室里的整合時間。

這些優勢結合起來帶給設計者更多的設計特色,并能縮短設計流程,加速產品上市時間(見圖2)。

在系統設計軟件里以同步仿真軟件為主,Atmel和Mentor Graphics合作開發的同步仿真軟件可以使得單片機、FPGA和SRAM同時在計算機上進行仿真。硬件描述語言(VHDL或Verilog)通過綜合驗證后可以用硬件仿真的軟件來實現仿真的功能(系統設計軟件里有Modelsim或任何一個支持Atmel產品的硬件仿真軟件即可),其軟件程序代碼(assembly或C語言)不僅可以用AVR Studio來仿真,也可以逐步作指令集仿真。同步仿真軟件提供軟件和硬件仿真的信息交流,支持單片機外圍設備和數據庫,且附加的功能(如外加的系統器件或通信接口)也可以很容易的形成,工程師在計算機里就可以進行系統級集成電路的設計和修改。

提供調試設計功能

除了同步仿真軟件以外,在系統設計軟件里還有其他的軟件可以幫助設計者完成系統級集成,然而這些軟件更注重于調試設計功能,HDLPlanner和EasyPlanner是以硬件描述語言 (VHDL和Verilog) 為主的軟件,它們不僅可以快速的幫助設計者完成程序,更有完善的功能可以縮短設計時間。HDLPlanner采用標準HDL模板,可以快速的完成代碼編輯,其功能有語法糾正模板、上下文加亮、集成用戶定義的元件等,通過和宏產生器相互連接,可以直接產生IP。EasyPlanner 是以畫圖和代碼合并的方式來幫助設計的,設計者通過點擊選擇想要的邏輯或功能,就可以直接產生相對應的器件描述語言。此外,EasyPlanner也支持宏產生器,可以直接將所選擇的邏輯進行布局布線,而且布局布線后有信息窗口打開,在里面可以看到其大小、速度、功耗等信息,設計者可以拿這些資料來評估此邏輯的適用度。

Atmel修改標準軟件

支持FPSLIC設計

Atmel修改了兩個標準軟件以支持FPSLIC設計。在FPSLIC的FPGA部分是用Atmel的IDS (Integrated Development System)來進行布局布線的,因此這一部分和原本FPGA軟件相同,從而可以讓使用者很容易的熟悉軟件環境,其功能包括:

?85%以上的自動布線工具

?層次化閱覽器

?結構映射

?底層規劃

?增量式設計

?輸出VHDL/Verilog 網表

?支持反向注釋

?幫助

?支持所有FPSLIC器件

它的另外一個軟件為AVR Studio 和 ISS (Instruction Set Simulator),Atmel把原有的AVR Studio加以修改以支持FPSLIC。AVR Studio軟件可以用來控制仿真,它會把“C”語言編輯的程序(用第三方編輯軟件,如IAR、 ImageCraft、Codevision或GCC)和/或原始代碼(如assembly)在其窗口里打開并進行仿真。在仿真過程中通用寄存器、存儲器、外圍設備、狀態寄存器和代碼都會一步一步的仿真并進行檢查,其功能包含斷點設定、寄存器和數據更改等功能。

而且,Atmel在系統設計軟件里設有軟件流程的標志,使用者在任何一個階段都可以知道下一步應該怎么做,其“檔案類別”跟不同的軟件步驟相連接,如VHD文件是和FPGA部分的設計入門、綜合驗證和仿真相連接,從而可讓設計者專心于設計上,而并不是軟件整合問題上。同時,系統設計軟件還可同時讓不同工程師在同一個設計里針對不同部分進行設計。

除此之外,Atmel提供的實時仿真的工具JTAG ICE,不僅可以仿真AVR,還可以延伸到 SRAM和FPGA接口,FPGA的實時仿真器目前正在測試當中,預計在2005年初將推向市場。

結語

在半導體領域,每十至十五年會產生一個好的產品和相應的軟件。十五年前FPGA把最先進的邏輯設計硬件和軟件帶給工程師創造了ASIC市場的革命,今天怎樣用系統級集成電路來簡化設計復雜性和電路集成成為了下一代科技的標準,一般完整的系統級集成電路的開發方案要十萬美元,但Atmel提供的芯片和其配套軟件,讓每一個工程師都能得到低價、靈活的設計機會。■

評論