下一代FPGA有望實現突破性優勢

本白皮書介紹為什么電信帶寬和基礎設施促進了FPGA功能的增強,以及ASIC和ASSP面臨的商業挑戰,可編程邏輯器件(PLD)定制方法是怎樣支持FPGA功能的跨越式發展。本文還簡要介紹了下一代FPGA和SoC系列品。

本文引用地址:http://www.j9360.com/article/283452.htm引言

最新發布的FPGA是硬件規劃人員、軟件開發人員和系統設計人員實現其下一代產品目標的關鍵支撐因素。大量的電信基礎設施成指數增長的帶寬需求以及各行業使用這些帶寬的需求使得現有硬件和軟件解決方案很難滿足性能要求,也難以達到成本和功耗目標。ASIC、ASSP和獨立處理器遇到了發展瓶頸,PLD公司很難解決固有的成本問題。而同時,大量最終應用對帶寬的要求越來越高,要求PLD公司通過不同的工具和選擇來滿足各種需求。通過這些選擇并且能夠高效應用它們的PLD公司將為硬件和軟件開發人員帶來突破性優勢,幫助他們開發下一代產品。

日益增長的帶寬和靈活性需求促使功能實現突破

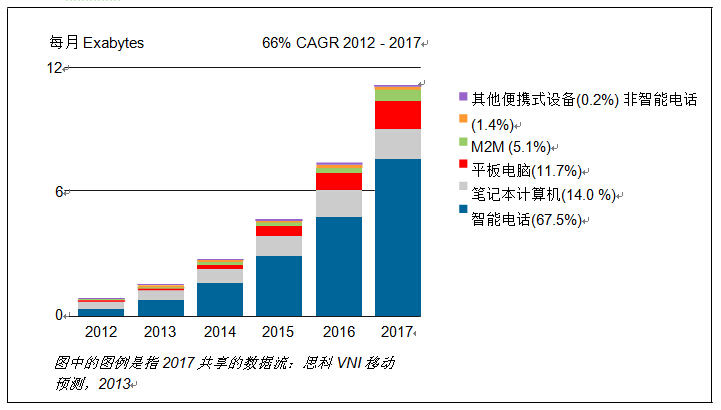

智能電話和其他便攜式設備越來越多的功能是促使系統性能大幅度提高的原因所在,下一代FPGA將體現這些系統性能。移動帶寬的爆炸式增長對無線、固網和數據中心體系結構功能產生了巨大的需求。智能電話數量增長速率呈個位百分比,而智能電話的功能越來越多,這些設備的用戶不斷要求提高帶寬。這主要是高質量視頻帶寬需求造成的。2012年,智能電話數據平均使用量增長了81%。思科預計到2017年,移動流量每年會增長66%,三分之二的移動流量是視頻內容。此時,移動網絡速度將會提高七倍,4G網絡承載了45%的流量(1) (參見圖1)。

圖1.思科預測到2017年,移動流量達到每月11.2 Exabytes

下面簡要介紹了三種基礎設施應用,在這些例子中,解釋了為什么硬件和軟件開發人員通過FPGA來實現其下一代產品帶寬、性能、功耗和成本目標。

■ 無線遠程射頻單元

■ 400G固網通道卡

■ 數據中心

無線遠程射頻單元

在大投入的無線基礎設施市場上,電信運營商要求帶寬更高更快,而成本更低。速度越快,運營商的成本就越低,就可以部署更多的系統,覆蓋更多的區域,為用戶提供更快的服務——這是很大的優勢。這些公司的產品策略是盡可能一直保持數據通路寬度不變,提高時鐘頻率。即將出現的遠程射頻單元將采用FPGA為復雜功能提供500 MHz內核性能,例如,實現數字預失真算法等。這保護了他們在射頻體系結構上的投入,支持他們覆蓋更寬的射頻(RF)帶寬。對此,他們尋求更好的投資回報,只需要很少的工作就能夠完成重新規劃解決方案。

而且,他們能夠很快獲得這些新產品,從而增強了產品及時面市優勢。他們還需要降低運營成本,降低每比特的成本,這是因為每一移動用戶的收入增長率要遠遠低于每一用戶的數據流量增長率。這樣,通過加寬數據通路,在更小而功效很高的FPGA上開發高功效設計,他們可以實現這一目標。

400G通道卡

提高FPGA性能的另一推動因素是更新網絡通信基礎設施的需求。下一代400G和現在的100G通道卡將極大的增強系統功能。下一代系統帶寬增長四倍,遠遠大于以前的系統。

這類市場處于起步階段,因此,公司不會冒險開發ASIC或者ASSP來實現這一目標。集成多個每秒56 gigabits (Gbps)和28 Gbps收發器解決方案可以滿足這一帶寬需求,但這只是解決方案的一部分。還需要更多、更快的邏輯來滿足更高的帶寬需求。但是,由于設備使用空間并沒有改變,因此,功耗指標受限。網絡基礎設施不會接受功耗隨帶寬線性增長的解決方案。對于400G帶寬每秒6億數據包的包處理和流量管理應用,調整數據通路寬度和頻率能夠緩解數據通路處理功能,但是無法調整調度等控制通路處理功能。因此,在各方面都需要提高器件性能,包括:處理、存儲器接口、IO接口,等等。FPGA一直是最吸引人的解決方案,但是公司要加大在每瓦高性能體系結構、收發器和工藝技術上的投入,大幅度增強功能,解決這一難題。

數據中心

通過這些新的無線設施上傳或者下載的所有數據和視頻會通過新的400G數據包處理基礎設施,也需要進行存儲和處理。計算功耗和計算成本是數據中心的關鍵指標。數據中心越來越多的使用了FPGA進行數據訪問、計算和網絡加速。數據中心服務器的瓶頸在于對數據的訪問。最新的處理器內核越來越多,但是,外部存儲器和數據帶寬卻跟不上計算能力的增長。很多服務器只達到平均利用率,距離峰值處理能力還很遠。這些服務器非常適合采用FPGA進行加速。通過FPGA實現硬件加速是替代這些處理器的好方法,它解決了處理器軟件無法克服的性能瓶頸。

其他應用也通過FPGA來滿足其越來越高的帶寬需求,例如,視頻內容提供商轉向4K視頻,還有云計算和國防情報應用等。這些應用面臨同樣的問題。如果需要了解詳細信息,請參考微軟研究:加速大規模數據中心服務的可配置架構。

ASIC和ASSP應用面臨越來越大的商業挑戰

ASIC設計需要很長的時間投放市場、很高的前端資金投入以及大批量產出才能實現回報等,這些因素使得ASIC的投入風險非常大,只有很少的公司會承擔這種風險。對于28 nm ASIC,ASIC工具模板和封裝的流片(NRE)成本、知識產權(IP)許可以及物理設計服務等成本很容易超過1千萬美元,在很多情況下,20 nm或者14 nm FPGA能夠解決這些問題。相對于ASIC,雖然目前的FPGA需要嚴格的仿真驗證,但是,與標準單元ASIC設計相比,實驗室測試以及能夠對FPGA重新編程等方法有效的降低了人工投入。FPGA組件價格雖然可能高于同樣復雜的ASIC,但是應該考慮總體擁有成本。標準單元ASIC的收支平衡點在不斷提高,前沿CMOS技術使得FPGA更復雜,性能更好,功耗更低,而這是ASIC難以實現的。

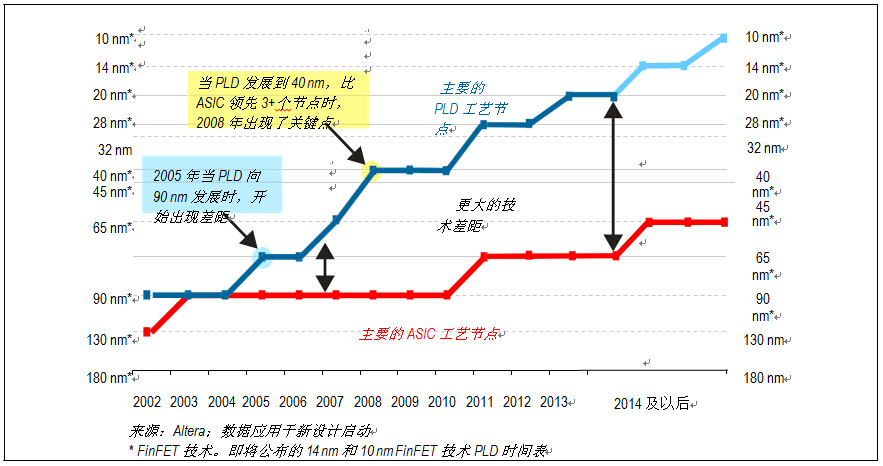

與FPGA和ASSP相比,低成本工藝節點會降低ASIC的優勢,這是因為這些解決方案會把客戶集中到更先進的工藝節點上,更具價格和性能競爭優勢。目前的FPGA使用28 nm工藝,很快將采用20 nm以及更小的工藝技術。但是,大部分新ASIC設計要落后兩到三個節點,甚至更多。差距越大,FPGA在價格、性能和集成度上就越具有吸引力。請參見圖2。

圖2.新設計的可編程邏輯和ASIC主要工藝節點對比

Gartner預測,到2016年,ASIC設計總數量每年會下降3.8%。而且,每過一年,每一設計都要求更高的產量才能獲得收益(3)。只有大公司能夠在市場上獲得ASIC成本回報,對于大部分公司,ASSP和FPGA成為唯一的可行選擇。

但是,ASSP價值地位也在下降,原因如下:

■ 提高處理器性能的挑戰

■ 突出產品優勢的需求

■ 響應市場的需求(產品及時面市)

■ 在可重新配置上不夠靈活

硬件規劃人員以前能夠借助越來越高的處理器頻率和越來越多的處理器內核來提高他們下一產品的系統性能。但是現在,由于處理器頻率并沒有隨時間大幅度增長,而是通過增加處理器內核數量以實現并行工作,無法解決性能瓶頸問題,因此,硬件規劃人員不能再采用這一方法來提高性能。很多硬件規劃人員的解決方案是開發專用硬件,以解決這些軟件瓶頸。

開發處理器使用的專用增強IP有助于解決這些難題。但是,競爭公司也可以使用讓ASSP優于前一代產品的硬件加速功能。此外,無法通過使用ASSP來解決某些特殊軟件的瓶頸。

ASSP的關鍵優勢在于產品快速面市,但并不總是如此。需要ASSP特殊功能的小公司無法獲得他們最需要的型號或何時將產品投放市場。大公司也得依靠供應商為他們提供所需要的產品。但是,他們能得到這些型號產品,其他公司也能得到。FPGA是克服這些ASIC和ASSP固有問題的好方法,在今后的產品中甚至能進一步增強功能。

評論