DSP推動3G移動通信革命

新近涌現的各種數字信號處理器(DSP)的規格尺寸繁多,外形各式各樣,令人難以勝數,其設計目標也是為了滿足各種對性能要求高低不同的應用。這些需求既包括附加在現有的處理器上、用于提供DSP功能的簡易編碼器,也包括可以驅動整個第三代蜂窩式電話的高性能器件。

本文引用地址:http://www.j9360.com/article/2809.htm早期的DSP主要用于數學運算。但后來它們的應用大大拓寬。其結果是,現在DSP也應用于以前專屬于微控制器的那些領域。在這些應用中,DSP所作的工作要比微控制器在同一領域中要重得多,因為系統現在靠一個處理器(DSP)工作,而非兩個處理器(DSP/微控制器組合)。

設計者也在改進其編寫代碼的方式。例如,現在有多種途徑可以實現一種特定的函數(如FFT)。處理器輸入數據,進行處理然后再輸出數據。兩種不同的算法可以產生相同的結果,但途徑不同,對運算能力的要求也大相徑庭。隨著工具的改進和設計者越來越適應DSP技術,這一現象也將得到改善。

由于DSP不象傳統的微處理器和微控制器的應用環境那樣成熟和確定,零售商就必須提供一攬子服務,包括軟件和開發工具,而不僅僅是芯片本身。這就是DSP供應商有別于其他供應商的一個方面——給系統設計者提供所需的全套軟件和工具,而不是把客戶推給第三方。在方便設計者的同時,這樣做也可以縮短基于DSP的產品推向市場的時間。

ARC是給現有產品添加一定程度DSP功能的多家廠商中的一家,只是所采用的方式有所不同。該公司提供了一個可定義的內核,而不是無法改動的硅片。用戶使用可定義的核時,可以將其拆散,并按完全不同的體系結構重組。因此,當一個設計者決定在他的處理器中添加DSP功能時,最終獲得的處理器從根本上來看將是全新的。

在使用一個固定的(如具有ARM或MIPS核)處理器時,添加DSP功能就要改變現有的體系結構,這就要求設計者學習新的軟件或工具。因此,這些廠商有必要與現有的技術保持一致。因為在ARM或類似的產品中,設計者對開發工具及其達到的性能水平已經熟悉和適應。但這也從根本上限制了設計,你不論添加什么,只能放置在核的外圍。真正的關鍵在于DSP協處理器(如果這是實現的方式)和主核間的帶寬。

用PLD(可編程邏輯器件)以搭積木的方式也可以實現DSP。在這種方法中,固定的功能一般下載到芯片中。這些功能可包括FIR 濾波、FFT和糾錯。顯然,PLD的功耗比傳統的DSP更多,但從所獲得的靈活性來看也是一種不錯的選擇。

Altera 公司的一位產品市場高級經理Justin Cowling說:“用一個PLD構建的DSP IP核可以取代電路板上的多個DSP,當你談論把幾個DSP放到電路板上時,功耗明顯高于單個PLD。我們已經建立了一個很大的功能固定的DSP功能庫。當一個客戶設計一個系統時,他只需畫一個包含多個DSP功能的方框圖。”

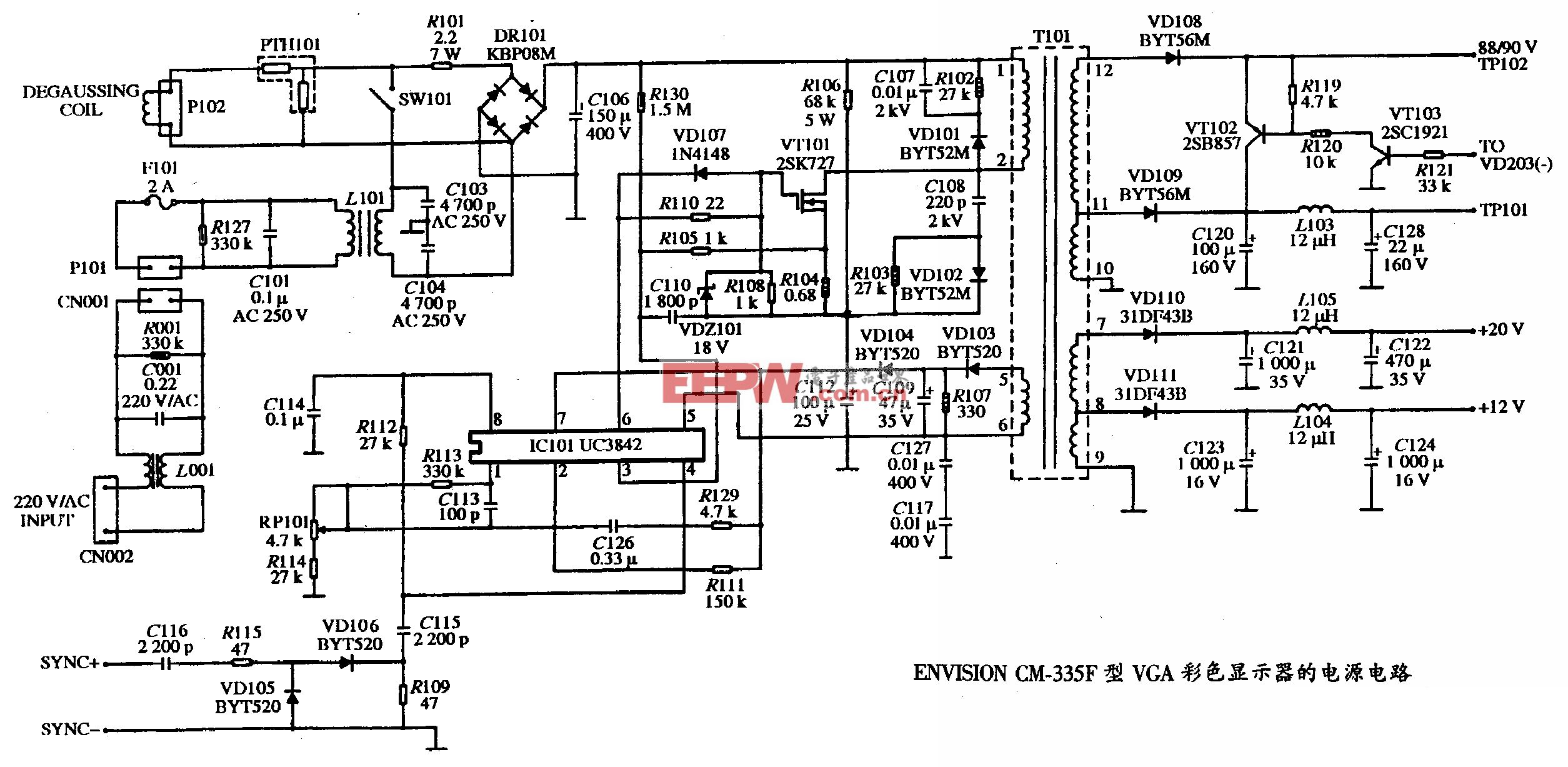

添加DSP IP對LSI Logic公司的工作人員來說是很自然的事。該公司提供低功耗的可以集成到一片ASIC中的DSP核。CW3000和CW3001兩種核均基于LSI ZSP400體系,分別在95和152MHz兩種頻率下工作(圖1)。ZSP400是一種完全靜態的核,可以接受高級時鐘管理和低功耗工作模式。這些低功耗模式使得非關鍵的外圍設備和系統時鐘可以采用軟件或外部中斷控制,而時鐘管理允許核在逐個周期基礎上避開無效邏輯的時鐘控制。

這種基于核的方法的優點在于開發者明白DSP核提供完全兼容的集成后,可以用符合ZSP標準的產品制作樣機。通過采用一個標準的系統總線(AHB),ASIC開發者可以選擇多種處理器, 如MIPS和ARM。

Analog Devices 公司(ADI)最近發布了一種屬于高端的DSP產品。所推出的Blackfin系列處理器基于一種特殊的核,而該核與Intel公司的產品一前一后推出。ADI宣稱這種核在DSP運算性能和功耗方面取得了突破。該系列處理器瞄準了“混合產品”,即組合了通信和運算功能的系統。系列中的第一款21535目前正在進行樣品展示。ADI認為,其優勢之一是有該公司的無線研發小組參與開發。這兩類研發小組的“雜交”應該能加快此類混合產品的推出。

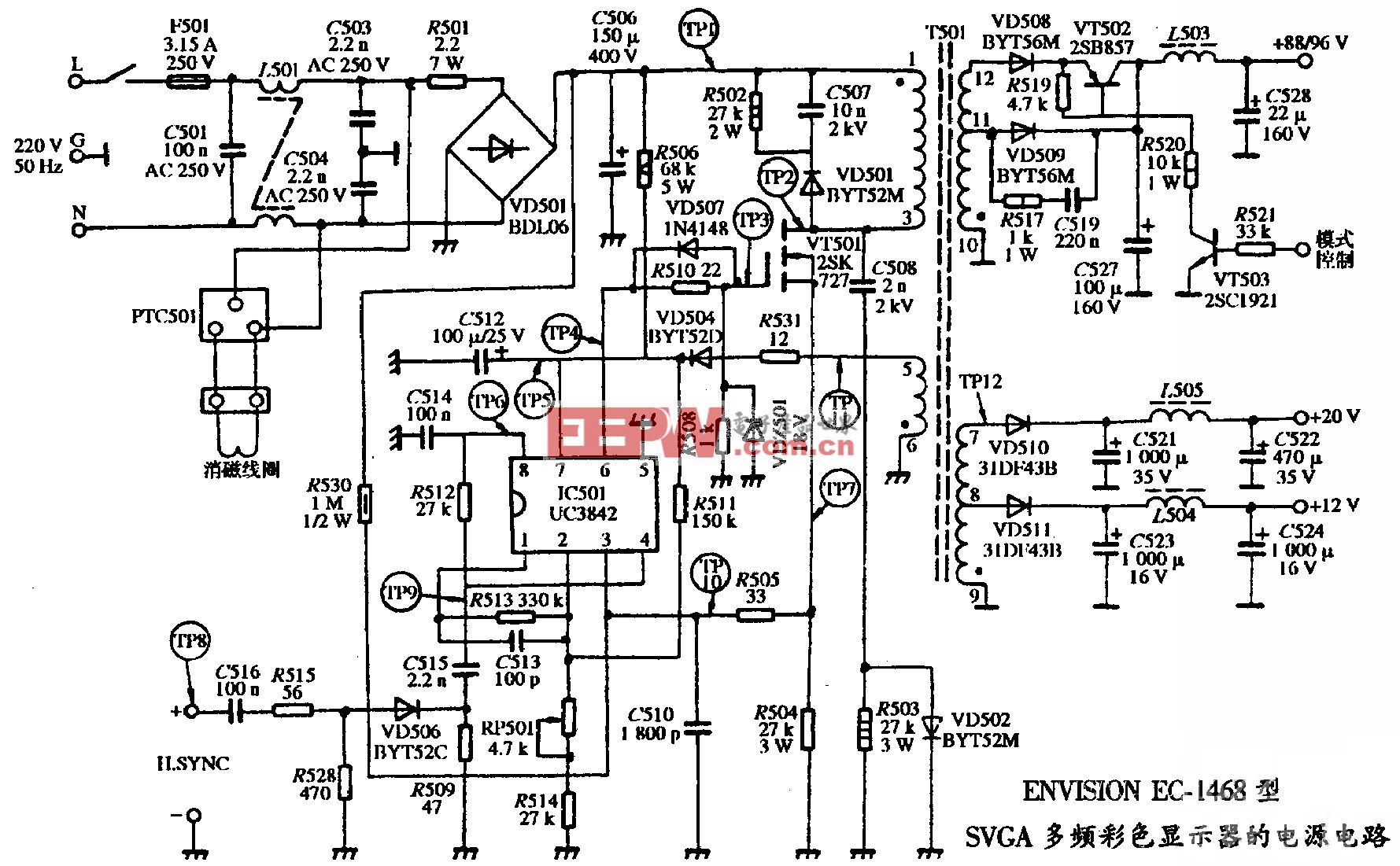

Blackfin產品采用了動態功耗管理。這意味著在運行中可以調整頻率和電壓,以使性能和電池壽命最優化。為了增強動態功耗管理,ADI開發了用于調節DSP電壓和頻率的芯片組。在核方面,ADI試圖很快將Blackfin技術的處理能力從目前的工作頻率300MHz和運算能力600M MAC(即每秒6億次乘法—累加操作)提高到工作頻率1GHz 和運算速度20億MAC。完整的21535具有豐富的外圍配置,包括USB和PCI接口,以及傳統的DSP類的外設(圖2)。產品系列中的下一代將針對特定的市場分區采用不同的外設配置。

如今一般的移動電話包含一個DSP和一個通用的處理器,如一個RISC處理器。這是因為有時在進行通用信號處理的同時還需要進行數字信號處理。例如,通過電話交談時需要用到聲音編碼、壓縮和其他DSP功能,同時用戶可能還要按鍵盤上的按鍵,并閱讀顯示的信息。由于DSP必須實時運算以防止丟失采樣點,因此對鍵盤和顯示的控制必須由通用處理器來進行。

TI公司的一位董事兼高級DSP開發部經理Ray Simar說,“幾年前,那些器件將是兩塊單獨的芯片——通用的RISC處理器和DSP,”現在,我們可以把它們集成在同一個封裝中。由于存儲器是內置的,它們在功耗方面占有優勢,面積也減小了。”

Simar接著說:“同時,電壓也下降了。功耗大致與電壓的平方成正比。如果你能始終降低電壓的量值,就可以大大減少功耗。這很令人感興趣,因為縮小裝置的幾何尺寸勢必要求我們采用更低的電壓,這與在DSP應用中降低功耗的需求相一致。”

在加快單個DSP—RISC處理器組合芯片研制進程的同時,TI和ARM最近宣布了一項協議:TI將獲得許可,在ARM v6體系結構基礎上開發IC。該結構體系是兩個公司兩年合作的結果,能使TI將其DSP與ARM的體系結構實現無縫連接。

ARM和TI兩家公司這一為期兩年的合作成果集成了雙方技術的一些新的特征,改進了數據同步、共享存儲管理并獲得更有效的OS操作。其目標是提高最終系統在運行實時聲頻和視頻程序時的性能,并保持低功耗。基于這種體系結構的產品將從ARM獲得,形式是合作商經過許可后可以在所設計的ASIC或ASSP中使用相應的知識產權(IP)核。

StarCore公司開發的內核應用于Motorola和Agere System公司的標準產品,他們相信自己的解決辦法適用于便攜式應用,因為其核的應用效率(用低功耗和緊湊代碼密度的組合定義)較高。與一些更為傳統的DSP供應商不同,StarCore的研究小組只專注于核的開發,完成后將核移交給Motorola和Agere的設計隊伍,來開發出標準的DSP產品。

為了在減小功耗的同時不至于降低性能,采用了傳統的節能模式,如關閉未使用的那部分處理器。內核也可以在運行中改變其工作頻率。

StarCore最新推出的SC140就是基于一個VLIW(超長指令字)類的結構。與前一代產品相比其改進之處在于:當指令調入執行單元時,無須使用OP指令。而且在分區指令方面沒有對準的限制。這不會減少對存儲器的讀取操作,而執行單元在不使用時不必加以時鐘控制。

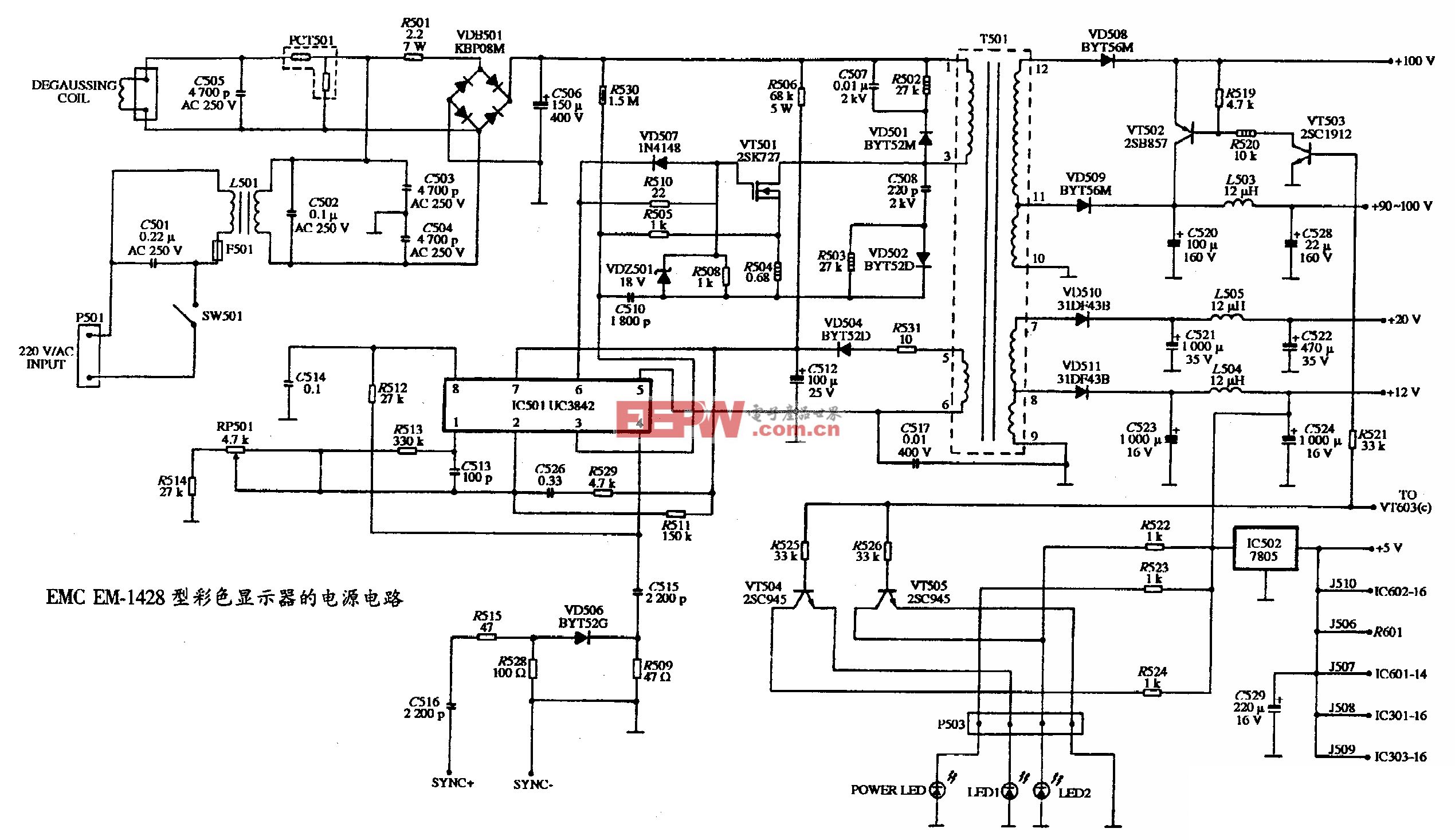

SC140可以在0.9~1.5V的電壓范圍內工作,在0.9V工作時,核可以達到120MHz的頻率。由于它是4MAC的結構,這就可以產生約480M MAC的計算速度(圖3)。核在0.9V時的峰值功耗,包括對存儲器的讀取,一般在40mW以下(假定每個執行單元在執行一條指令,典型應用中并不總是這種情況)。

“對于一個典型的無線裝置來說,我們希望它在盡可能接近1V的條件下工作,”StarCore公司一位市場總管Scott Beach說,“但對于一個高端系統,如3G系統來說,你可能要讓它在1.5V下工作,才能使工作頻率接近300MHz。”

StarCore體系結構的一個設計目標是確保兼容性,使得用戶可以用C編譯器開發大多數代碼。“從編譯的角度來看,關鍵在于編譯人員要協助確定有多少個寄存器,并確保體系結構的各個不同的方面相互一致,從而保證編譯器能利用這一點,并生成有用的代碼。”Beach解釋說,“我們的目標是讓編譯器開發并生成有用的代碼,從而只需極少的手工優化工作。”

StarCore 新近宣布了一項與Wind River System公司的協議,為基于DSP的系統芯片(SoC)嵌入式應用建立一個集成的軟、硬件開發平臺。該平臺將把Wind River的嵌入式軟件和開發工具與最新的StarCore的DSP技術結合起來。根據該項協議,Agere、Motorola和Wind River將對Wind River的實時操作系統(RTOS)和用于StarCore體系結構的開發工具進行優化,以方便無線通信裝置的開發。

Wind River將開發并提供一個C/C++編譯器和一套運行分析軟件、一個針對StarCore 的源程序級調試器和硬件調試工具,以協助早期的硬件和未來Tornado集成開發環境的研究。■(繆民譯自《Portable Design》2001,9)

評論