探索ARM Cortex-M7核心:為明日物聯網預做準備

如果嵌入式內存訪問速度與所需的處理器速度相近,則嵌入式閃存可以和具有一些閃存訪問加速的ITCM接口連接。而在其他情形中,使用帶有緩存的AXI將更加合適。如果應用需要從外部內存控制器執行程序,那么內存控制器通常會與AXI接口連接,也就需要指令緩存和數據緩存的支持。在一些情形中,應用可能只需要將外部內存用于數據存儲。這樣的情形中不需要指令緩存。

本文引用地址:http://www.j9360.com/article/277715.htm

選擇緩存大小很大程度上取決于應用程序代碼的屬性。在嵌入式閃存運行程序代碼時,會同時利用指令緩存和數據緩存,因為程序映像通常會隨指令一起包含文字數據、查找表或只讀常量。與程序映像內部中的數據/常量相比,應用程序通常有更多指令字。隨著程序大小變大,緩存要求也在提高,指令緩存大于數據緩存也不罕見。相反,一些應用程序可能有很小的控制或DSP循環,同時可能有大量的數據用作計算的系數。在此類情形中,較大的D緩存可能比較大的I緩存更對系統性能有益。

當然,進行性能優化時,也需要最大化緩存以確保較大代碼和數據大小的最低延遲性。不過,通過以等同于處理器的速度運行大緩存內存,可能會根據其他因素而造成緩存查找消耗大量的功率。此外,大多數應用程序的緩存未命中率曲線隨著尺寸增大而向零靠近,這意味著進一步增大緩存大小并不會提高性能。所幸的是,Cortex-M7 核心的可配置性使得 SoC 架構師能夠整合各種各樣的緩存尺寸,從無緩存到最高64KB的指令緩存和64KB數據緩存。借助這樣的靈活性,設計人員可以調節SoC來滿足目標應用的需求。

除了架構選項外,Cortex-M7處理器上的許多其他功能也可加以配置。例如,SoC的浮點單元(FPU)功能可以配置為完全不含FPU、具有IEEE-754單精度浮點運算的FPU,或者同時支持IEEE-754單精度運算和雙精度運算的FPU。

其他配置功能包括:

● 中斷數、以及 NVIC 中的優先級別數;

● 內存保護單元(MPU)配置;

● 調試與跟蹤功能;

● 功能安全性相關的功能(ECC、雙核鎖步)。

浮點運算硬件加速有諸多優點。顯而易見,具有硬件浮點單元時浮點運算的性能可以得到加速。此外,由于硬件支持減少了執行浮點運算所需的軟件庫數量和相關大小,因此內存空間也得以優化。縮短處理時間并且減少內存足跡最終提高應用的能效,為執行傳統上需要更多復雜嵌入式系統的功能掃清了障礙。這種優勢對能效而言非常重要,因為 DSP過濾器的浮點運算最高可提速 20 倍。同時具備單精度和雙精度浮點功能選項可進一步提高新款處理器的可擴充性。

隨著IoT的演進逐步帶來技術的擴充,應對嵌入式應用的安全性和完整性挑戰的需求也在增長。除了與其他 Cortex-M 處理器相同的錯誤異常處理功能和內存保護單元外,Cortex-M7 處理器也包含可選的TCM內存和緩存錯誤校正代碼(ECC)支持。這可以實現自動即時更正內存中的單比特錯誤、以及檢測雙比特錯誤。

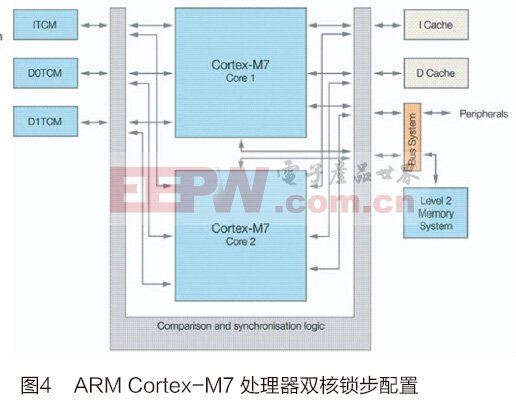

此外,Cortex-M7處理器也支持雙核鎖步配置選項。在這種配置中,核心邏輯進行兩次實例化,緩存和TCM內存陣列則是共享的。這是因為它們可以通過ECC加以保護,其硅面積成本能大幅降低(見圖4),實現非常強健的容錯系統設計。

飛思卡爾Kinetis KV5x MCU系列的實現

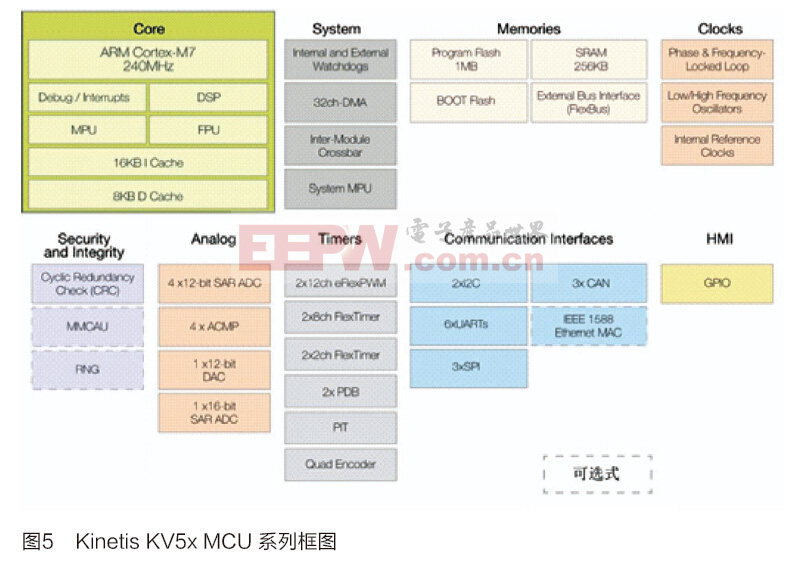

Cortex-M7處理器的一個實現選擇示例是飛思卡爾最新發布的Kinetis KV5x MCU系列,這一可擴充的MCU產品系列定位是面向電機控制和數字功率轉換應用。在這一SoC中,Cortex-M7處理器選擇的部分配置選項包括整合16KB指令緩存和8KB數據緩存。此SoC將64位AXI總線用作嵌入式閃存存儲器的訪問端口。指令緩存和數據緩存確保駐留于嵌入式內存中的控制軟件得以加速,支持所連的工業級控制用例所需的性能級別。除了緩存之外,Kinetis KV5x MCU系列還集成了64KB與ITCM接口連接的 SRAM、以及128KB與DTCM接口連接的SRAM。這可提供必要的處理器本地存儲,以延遲性最低的內存支持實時控制運算。

Kinetis KV5x MCU配置僅僅是一個示例,說明了如何構建SoC以應對關注于聯網控制的特定應用。隨著時間推移、以及互連應用數量和多樣性的增加,未來必定會出現對SoC 設計的調節,從而在Cortex-M7處理器上進行更廣泛范圍的配置。性能水平與可比較的 Cortex-M4解決方案相比將可達到兩倍以上的提高,這將為嵌入式領域實現更多的創新。憑借其可擴充性、性能和可擴展功能,可調節型Cortex-M7核心將在支持“明日物聯網”的舞臺中扮演重要的角色。(本文全文刊登在電子產品世界網站)

物聯網相關文章:物聯網是什么

評論