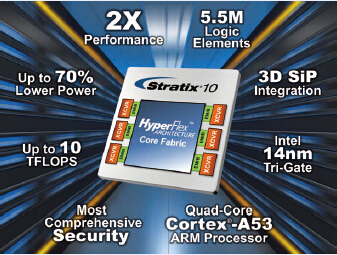

Altera宣布Stratix 10的創新:FPGA和SoC性能翻番、功耗降低70%

即將于2015年秋天提供Stratix 10 FPGA和SoC工程樣片的Altera公司,近日發布其Stratix 10 FPGA和SoC體系結構和產品細節,在性能、集成度、密度和安全特性方面實現了突破。

本文引用地址:http://www.j9360.com/article/276719.htmStratix 10 FPGA和SoC采用了Altera革命性的HyperFlex FPGA架構,由Intel 14nm三柵極工藝技術制造,內核性能是前一代FPGA的2倍。性能好、密度高、具有先進的嵌入式處理功能的FPGA與GPU類浮點計算性能和異構3D SiP集成特性相結合,支持Altera客戶解決下一代通信、數據中心、雷達系統、IoT基礎設施和高性能計算系統中所遇到的設計難題。

Altera公司產品營銷資深總監Patrick Dorsey詳細介紹了HyperFlex體系結構的“寄存器無處不在”方法。Stratix 10 FPGA和SoC是第一款采用公司的HyperFlex新體系結構的Altera器件。HyperFlex的核心是減少了關鍵通路,例如,當一個功能要和另一個功能進行溝通時,通常是在幾個納秒之內。所謂系統性能,實際上體現在進行通話過程中出現的最長延時,例如3.5納秒的延時。HyperFlex的優勢在于把這3.5納秒時間間隔切成三段,例如其中有一段是1.2納秒,表明其性能實際上是得到一個很大的提高,即頻次得到了降低,因此性能得到了提升。可以用一個形象的比喻:現在所有人都要開車通過一架大橋,但這架大橋的設計一次只允許通過一輛,如果有100輛車,你必須一輛輛通過。HyperFlex相當于你把這架橋建得更短了,建成很多小橋,使汽車通過的速度得到了很大提升。可見,“yperFlex體系結構幫助設計人員避免了關鍵通路和布線延時,其設計能夠迅速達到時序收斂。內核邏輯性能提高2倍后,不需要很寬的數據通路,也不需要競爭體系結構由于其他偏移導致的設計結構,極大地提高了器件利用率,降低了功耗。HyperFlex體系結構支持高性能設計降低邏輯面積要求,功耗從而降低了70%。”

fpga相關文章:fpga是什么

評論