一種低誤碼率的ADS-B接收機的設計

摘要:針對廣播式自動相關監控(ADS-B)接收機存在高誤碼率的問題,設計一種基于FPGA的ADS-B接收機,通過ADC電路轉換解調后的模擬信號為數字信號,并利用FPGA的并行處理的特點,采用流水線方式處理ADS-B信號;利用有關數字濾波和數字信號提取算法,計算得到ADS-B信息,并經過PL2303HX發送電腦上位機中。實驗結果證明,可以較好地完成1090MHz ES ADS-B信號的接收,實現了內部數字信號濾波算法和CRC校驗,有效地降低設備的誤碼率。

本文引用地址:http://www.j9360.com/article/274749.htm1 序言

廣播式自動相關監視(ADS-B)是一種基于GPS全球衛星定位系統和空-空、地-空數據鏈通信的航空器運行監視技術[1],正在逐漸成為空中交通管制的一種重要監視手段。ADS-B技術將衛星導航、通信技術、機載設備以及地面設備等先進技術相結合,提供了更加安全、高效的空中交通監視手段,能有效提高管制員和飛行員的運行態勢感知能力,擴大監視覆蓋范圍,提高空中交通安全水平、空域容量與運行效率[2]。本文介紹了一種基于FPGA的1090MHz ES ADS-B的設計方法,通過ADC采樣解調之后的信號,并通過數字濾波的方法濾除干擾信號,得到真實信號,利用相關的解算算法,提出ADS-B中的信息,并將其發送到上位機中。

1.1 ADS-B消息格式

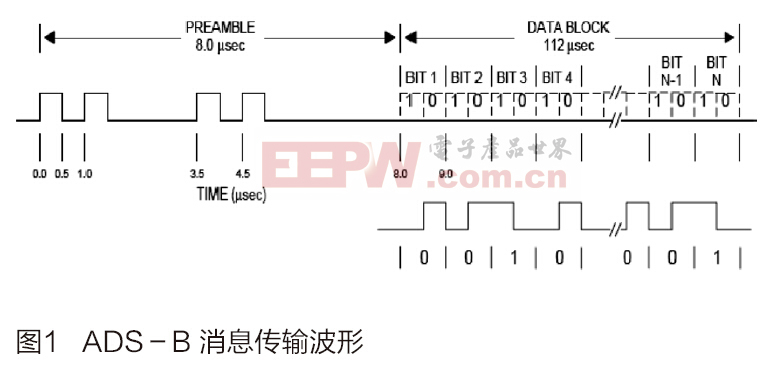

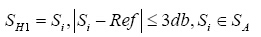

1090MHz ES ADS-B消息包含了四個識別脈沖信號和112位或56位的消息序列。ADS-B消息數據編碼格式采用脈沖位置調制(PPM)編碼,如圖1所示。

1.2 消息提取算法

ADS-B的消息提取采用振幅比較的方法,在該接收機中,采用了10MSPS的采樣速率,所以每個信息位前、后時間位置脈沖分別采樣5次 [3] 。

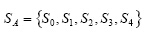

(1)將信息位前時間位置的采樣集合命名為 ,后時間位置采樣集合為

,后時間位置采樣集合為 ;

;

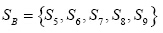

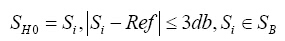

(2)計算出SA,SB內在參考功率Ref正負3dB之內的所有采樣點:

其中Ref為參考功率,即每個信息位的10個采樣點相近振幅最多點的集合;

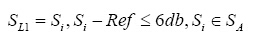

(3)計算出SA,SB內參考功率小6dB以上所有采樣點集合:

(4)對以上四個集合的點進行加權運算,考慮到本系統FPGA的性能,所有權值均為整數,其中點S0、S4、S5、S9運算權值是1,點S1、S3、S6、S8運算權值是2,點S2、S7 的運算權值是3,則求的四個運算結果分別為A、B、C、D;

(5)對以上四個運算結果再次做如下運算:

R1= A-B+C-D

R2= B-A+D-C

若R1>R2則該信息位為“1”,否則信息位的值為“0”。

1.3 數字濾波

為了消除ADS-B信號中的雜波,這里采用圖像應用中的中值濾波算法。中值濾波的原理是將序列中一點的值,用該點領域內各點值的中值來代替[4] 。

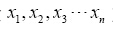

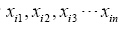

假設 為一組信號序列,按照其大小排序為

為一組信號序列,按照其大小排序為 ,則計算得到其中值數值y是

,則計算得到其中值數值y是

以上公式中,在一維情況下,中值濾波器是一個含有奇數個采樣點的滑動濾波窗口[4] 。則濾波器的輸出信號序列為:

。

。

2 硬件設計

2.1 系統設計

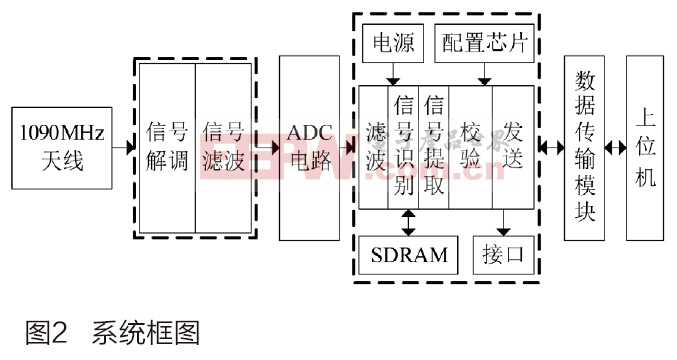

接收機通過1090MHz 天線接收ADS-B的信號,并通過解調設備,得到解調信號,采用FPGA作為核心處理器,通過AD9233高速ADC轉換芯片采集信號,在FPGA中解算提取相關信息。其設計框圖如圖2所示。

2.2 前端硬件設計

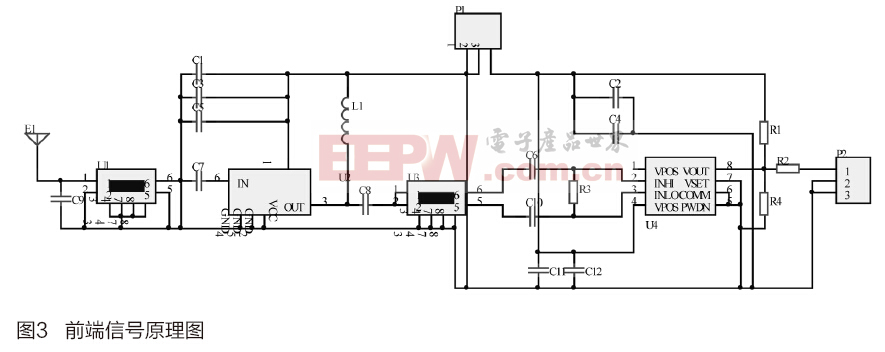

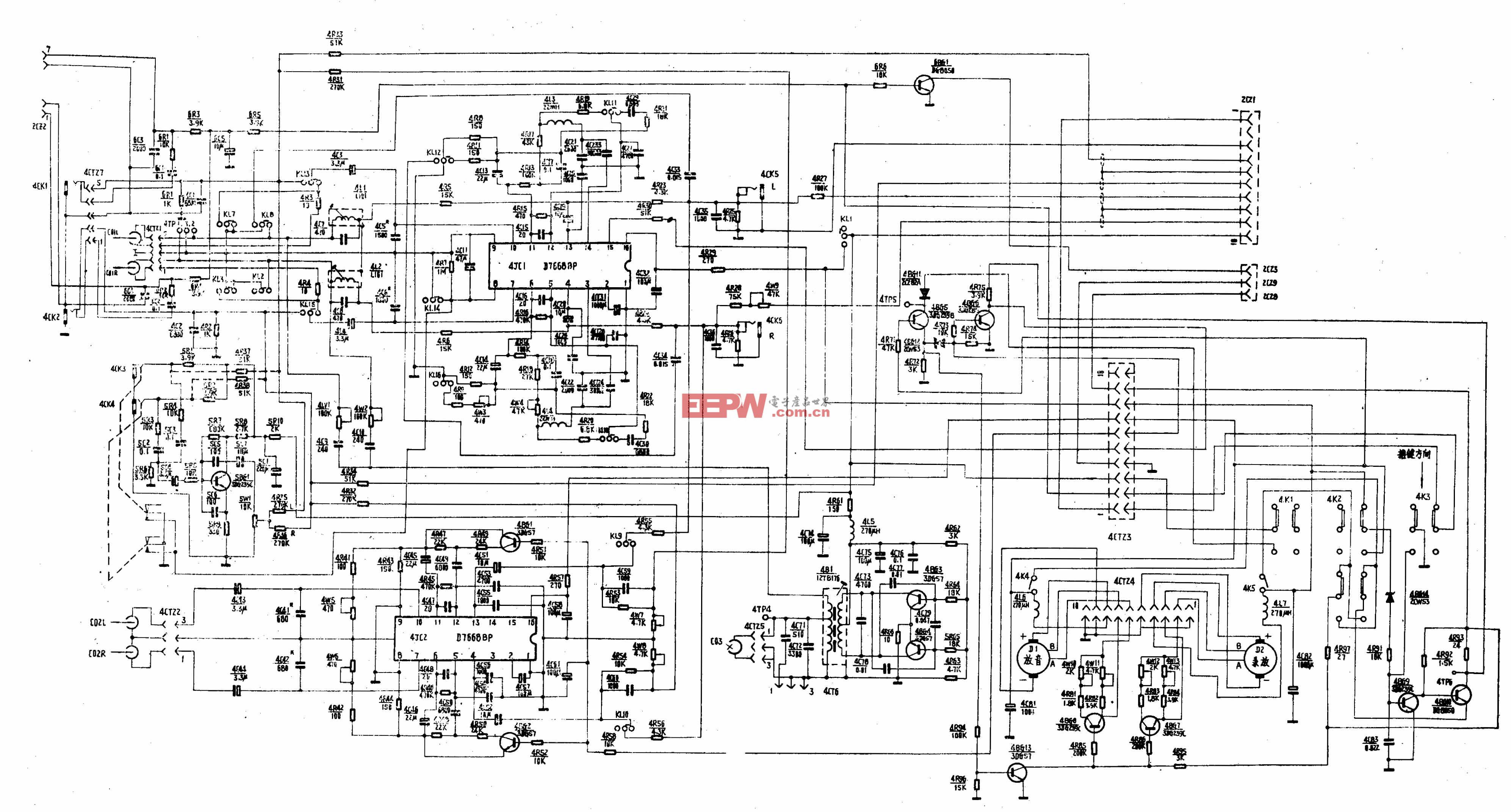

前端設備采用了TA1090EC、BGM1013、TA0232、AD8313芯片,實現濾波和解調的功能,由于后端采用ADC轉換電路,所以此處不需要轉換為TTL電平信號,最大程度保證信號的完整性和真實性,提高解碼的高效性和降低誤碼率。原理圖如圖3所示。

2.3 ADC電路設計

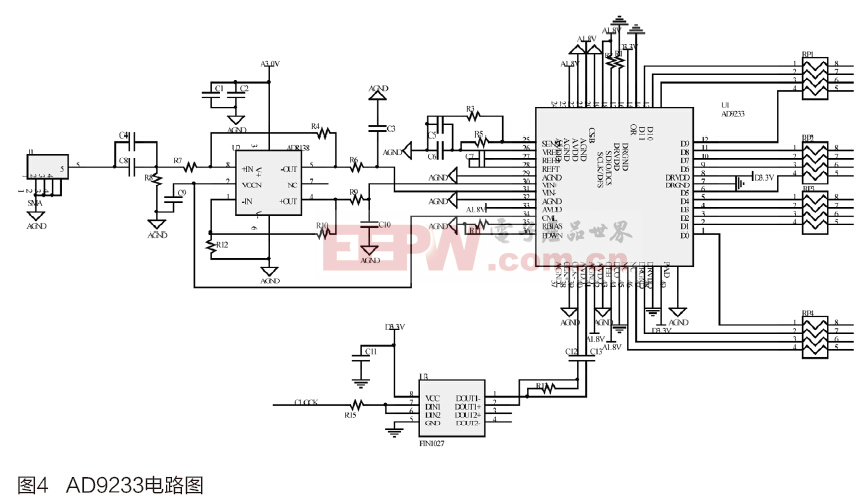

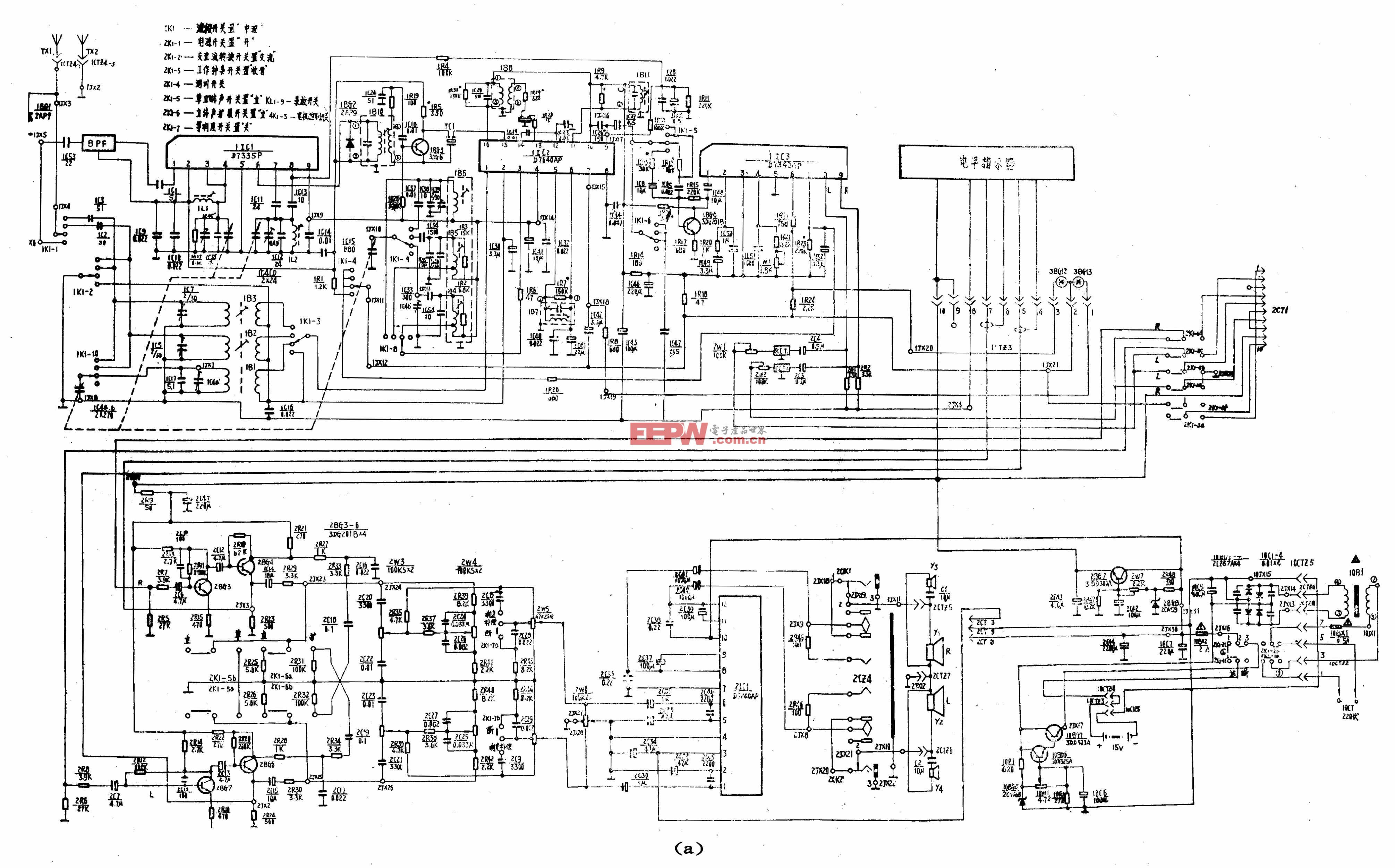

ADC采樣電路需要滿足10MSPS的采樣速率,并且需要保證信號的適當幅度。在這個模塊中,采用了ADI公司的AD9233芯片(電路圖如圖4),其采樣頻率可以達到125MHz,大大提高ADS-B接收機的信號采集效率;其分辨率為12位,能夠很好地識別小信號,還原真實信號,為后面的數字濾波提供數據。

2.3 FPGA電路設計

ADS-B信號的濾波和解碼都是通過FPGA實現的。FPGA電路采用Altera公司的EP4CE6E22C8N的芯片,外部通過AMS-1117系列的電源芯片實現3.3V、1.2V、2.5V的供電,并采用EPCS4SI8N作為FPGA的配置芯片。整個系統采用外部有源晶振50MHz作為系統時鐘,并通過時鐘分頻產生ADS-B信號的采樣和串口發送的時鐘信號。并預留了JTAG和AS的下載接口,以便實現FPGA的調試和下載。整個FPGA在ADS-B接收機中起到了信號的數字濾波、信號報頭識別、信號提取、CRC校驗、信息轉換為ASIC II碼和信息的發送等功能是ADS-B接收機的核心。

模擬信號相關文章:什么是模擬信號

晶振相關文章:晶振原理

評論