PCB層級中時序交錯式超高速ADC解決方案

運用時序交錯式類比數位轉換器(timeinterleavedADC)在每秒高達數十億次的同步取樣類比訊號是一個技術上的挑戰,除此之外,對於混合訊號電路的設計也需要非常謹慎小心。基本上,時序交錯的目標是利用轉換器數目與取樣頻率相乘而不影響解析度以及動態的效能。

本文引用地址:http://www.j9360.com/article/274410.htm本文將探討運用時序交錯式類比數位轉換器時所出現的技術挑戰,并對此提供實用的系統設計解決方案。本文也將說明可以解決目前已知問題的創新元件的特色及設計技術。同時利用快速傅立葉轉換(FFT)計算法算出7GSPS速率及兩個轉換器晶片在「交錯解決方案」下的結果。最後將說明為達成高效能所需的時脈源及驅動放大器之支援電路圖應用。

需要更高的取樣速度

何時以及為何增加取樣的頻率是具有優勢的呢?有多個答案可以回答這個問題。基本上,類比數位轉換器的取樣速度會直接影響到瞬間頻寬,因為瞬間頻寬會在取樣的瞬間被數位化。根據Nyquist與Shannon的取樣定理表示,最大允許的取樣頻寬(BW)等於取樣頻率(FS)的一半。我們可以用以下的方程式表示:

BW=FS/2

速率為3GSPS的類比數位轉換器能在一個取樣周期內取樣15億赫茲的類比訊號頻譜。讓取樣速度加倍的同時也會讓Nyquist頻寬加倍成為30億赫茲。藉由時序交錯使取樣頻寬產生增加的結果對於很多應用提供相當的助益。舉例來說,應用時序交錯的無線電收發機架構就可以增加資訊訊號載波的數目,使得系統資料處理能力得到提升。增加取樣頻率同時也可以改善LiDAR測量系統(LiDAR系統依循飛行時間(TOF)原理而運作)的解析度。基本上,飛行時間測量的不準確度可以經由減少有效取樣時脈周期的方式而降低。

數位示波器也需要較高的取樣頻率對輸入頻率(FIN)的比值,才能更精準的獲得復合式類比或數位訊號。取樣頻率必須是FIN的最大值的數倍以上才能得到FIN的調和成分。舉例來說,如果在示波器取樣頻率不夠高的情況下,若較高位階的調和頻率在類比數位轉換器Nyquist頻寬的范圍之外,那麼原本的方波將會變成正弦波的形式。

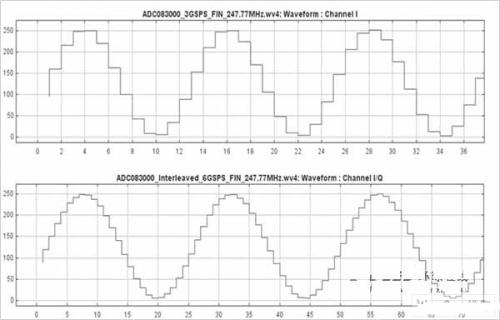

圖1:在速率3GSPS及速率6GSPS時針對247.77百萬赫茲訊號取樣的時域測量波形圖。

圖1所示為示波器前端加倍取樣頻率所產生的優勢。取樣類比輸入訊號中速率6GSPS的取樣波形將得以更精準地呈現出來。許多其他的測試儀器系統,比方像是質譜儀以及伽瑪射線望遠鏡都是依賴較高的過度取樣與輸入頻率的比例來達成脈沖形狀的測量。

增加取樣頻率還可以獲得其它的優點。過度取樣的訊號也能對數位濾波的過程中得到增益有所助益。基本上,類比數位轉換器的雜訊底部擴散涵蓋大部分的輸出頻寬。對一個固定的輸入頻寬采用兩倍的取樣頻率進行取樣,能在動態范圍中獲得3dB的改善。而每一次對取樣頻率進行加倍也都能讓動態范圍額外獲得3dB的改善。

時序交錯所面臨的挑戰

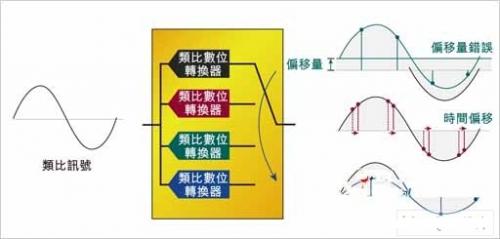

時序交錯主要面臨的挑戰為頻道間做取樣時脈邊緣的精確相位校準,以及在積體電路之間與生俱來的制造變數補償的問題。為了能精確的與增益匹配,各個分別類比數位轉換器間的偏移量與時脈相位都將十分重要,特別是與頻率有關的參數更顯重要。除非這些參數能夠達到精確匹配,才能使動態效能與解析度得以降低。圖2所示為三個主要的錯誤來源。

圖2:交錯是類比數位轉換器在增益、偏移量、時序上的錯誤。

一般而言,雙通道交錯轉換器的系統需要類比數位轉換器的輸入端取樣時脈產生1/2個時脈周期的時間平移。然而ADC083000類比數位轉換器的架構則使用晶片本身具備的交錯技術,并以時脈頻率相當於取樣率一半的數值進行運作,也就是說使用1.5GHZ的頻率來對應3GSPS的速率。因此對於采用兩組ADC083000類比數位轉換器的雙通道系統而言,類比數位轉換器輸入取樣時脈邊緣必須是1/4個時脈周期的時間平移或是與其他邊緣產生90°的角度平移。對於頻率1.5GHZ時脈而言,相符合的數值為166.67ps.

時脈訊號的線路長度可以經由計算方式精確地得到1/4個時脈周期的相位平移。在FR-4的印刷電路板材料中,訊號可以20cm/ns的速率來傳遞,即每50ps傳遞1公分的距離。舉例來說,如果到一組類比數位轉換器的時脈路徑比另一組長3公分以上,那麼將會產生150ps的相位平移。要如何精確地達到額外16.67ps的時間平移將會是要面臨到的挑戰。

ADC083000類比數位轉換器具有一個整合型的時脈相位校準功能,這個功能可以讓使用者在輸入取樣時脈中加入一個延遲來平移其相位以便與另外一個類比數位轉換器取樣時脈建立關聯性。類比數位轉換器的時脈相位可以經由內建的兩組暫存器透過SPI匯流排進行手動校準。其中的相位平移只可能發生在一個方向上來增加延遲現象。設計人員需要來決定這兩組分離的類比數位轉換器中的哪一組是「在前方的」,并校準其相位使取樣邊緣與另一組類比數位轉換器的取樣邊緣端間產生90°的角度差。以提供Sub-picosecond等級的校準解析度。

通道對通道的增益與偏移量匹配

在一個具備雙轉換器的交錯系統中,假設輸入訊號在第一Nyquist范圍內時,因為通道增益不匹配所產生的錯誤電壓值會造成在FS/2–FIN與FS/4+/-FIN位置上的影像突波。一組8位元的轉換器擁有28或256個編碼。假使轉換器的完整輸入范圍是1V的峰值對峰值,LSB的大小會等於1V/256=3.9mV的數值。而我們也能精準的計算出對於1/2LSB所需的增益匹配值為0.2%.

ADC083000類比數位轉換器的輸入端完整電壓值或增益能用9位元資料值來進行線性及單調的校準。700mVp-p的差異值可校準的范圍為±20%,也就是說可校準的范圍在560mVp-p到840mVp-p之間。

840mV–560mV=280mV

29=512steps.280mV/512=546.88uV

微調校準的角度可允許超過上述的0.2%增益匹配范圍。

在相鄰通道間的偏移量不匹配會產生一個錯誤的電壓值,這將會造成在FS/2位置上的偏移量突波。由於偏移量突波是發生位於Nyquist帶的邊緣,因此雙通道系統的設計人員通常要規畫他們所需的系統頻率并將更大的心力著重於增益與相位匹配上。

然而,讓我們假設所需要的偏移量匹配也等於1/2的LSB基本標準值時,ADC083000類比數位轉換器的輸入端偏移量能透過線性及單調的校準,在9位元解析度中使0偏移量增加到45mV的偏移量。因此每一組編碼位階都提供了0.176mV的偏移量,同時9位元的解析度可以協助達成1/2LSB基本標準值的精確性。

數位輸出的同步

將兩組類比數位轉換器的輸出資料串進行同步有助於實現混合的取樣速度與頻寬。換句話說,如果在兩個獨立的轉換器之間發生同步損失的話,那麼我們將無法獲得有意義的資料。數以十億計的取樣類比數位轉換器「解多工」輸出資料來降低數位輸出資料的速率。使用者可以依據所采用的FPGA技術對於資料處理的能力來選擇用2或4的資料速率來「解多工」。

輸出擷取時脈(DCLK)也可以被分割并設定為SDR或是DDR模式。然而對於解多工的方案,由於在每一個類比數位轉換器的輸入取樣時脈與輸出擷取時脈間的聯系,這使得整個系統存在一些不確定的因素,因此設計人員需要考量更多。為了解決這個問題,ADC083000類比數位轉換器有能力藉由使用者供應的DCLK_RST脈沖,來精確的重置其取樣時脈輸入到輸出擷取時脈輸出之間的關系。這項能力能夠讓系統中多個類比數位轉換器同時擁有各自的輸出擷取時脈(以及資料)輸出轉換,并且可以共同分享輸入時脈以便進行取樣,同時,這將使得多個類比數位轉換器之間的同步可以達成。

數位交錯技術

類比校正法是一種已被證實能傳遞高動態范圍、具備整合能力的解決方案,這個解決方案具備整合性時脈相位、增益與偏移量校準的功能,且已被證明能提供高精確度。

除了類比校正技術之外,還有其他幾種可行的方法,舉例而言像是數位校正演算法也可用來處理交錯資料。這幾種處理方法都能在不需要任何類比偏移量、增益或是相位校正的前提下,能校正資料轉換器中數位不匹配的問題。在理想狀態上,這些演算法都不需要對輸入訊號做任何校正或是先有基礎的觀念就能夠獨立運作。除此之外,在數位偏移量、增益及相位校準所需的時間則是系統最重要的運算因子。

由SP元件公司所發展的數位後制處理引擎(這也是一套演算法)就能滿足上述的這些需求。SP元件公司的自動數據交換(ADX)技術,在不需特殊校正訊號或後期制作整理的條件下,會持續提供類比數位轉換器在增益、偏移量與時間偏移錯誤的估算。而這種演算法已經應用於修正靜態與動態上不匹配錯誤的問題。

ADX技術能估算錯誤并依據所有不匹配錯誤來重建訊號。IP核心的錯誤校正演算法,能在不限輸入訊號型式的前提下有效的執行。數位訊號處理的結果為ADX核心之外的時序交錯頻譜在與交錯失真突波相關處不會出現明顯的不匹配錯誤。

評論