基于FPGA和51單片機的信號發生器設計

信號發生器又稱為波形發生器是一種常用的信號源并且廣泛應用于電子電路、通信、控制和教學實驗等領域的重要儀器之一。為了降低傳統函數信號發生器成本,改善信號發生器低頻穩定性。筆者結合FPGA和51單片機產生0.596 Hz頻率精度函數信號。筆者設計通過51單片機控制函數信號類型以及相關參數,用戶可通過按鍵設置需要的波形、波形幅度、波形頻率以及方波的占空比、相位。本文設計方案不僅具有良好的經濟前景,也可以為當代高等教育深化改革做一個參考方向。

本文引用地址:http://www.j9360.com/article/273790.htm1 系統設計方案

1.1 系統硬件設計

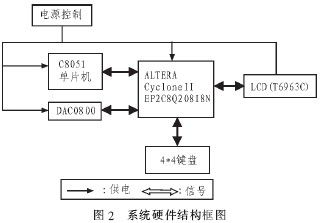

本文中設計中硬件包括EP2C8Q20818N芯片和C8051F0201單片機、DAC0800芯片,T6963的LCD。本文中主要利用FPGA(EP2C8Q20818N)橋接控制LCD、4×4鍵盤和DAC0800(C8051單片機和DAC0800有一條基準電壓信號),系統硬件設計框圖如圖2所示。本文中函數信號主要由FPGA(EP2C8Q20818N)產生;C8051單片機用作分析處理用戶信息、給DAC0800提供基準電壓以及控制FPGA(EP2C8Q20818N)產生需要用戶的函數信號。

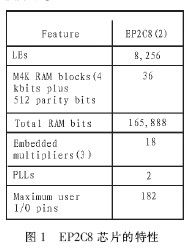

1.1.1 EP2C8Q20818N簡介

EP2C8Q20818N是ALTERA公司推出一款嵌入式FPGA(現場可編程門陣列)芯片。具有182管腳。下面列出它的特性表,如圖1所示。

1.1.2 C8051F0201簡介

C8051F0201(以下簡稱51單片機)器件是完全集成的混合信號系統級MCU芯片,具有32個數字I/O引腳。此款51單片機具有高速、流水線結構的8051兼容的CIP-51內核(可達25 MIPS)。全速、非侵入式的在系統調試接口(片內)。12位、100 ksps的8通道ADC,帶PGA和模擬多路開關。8位500 ksps的ADC,帶PGA和8通道模擬多路開關兩個12位DAC,具有可編程數據更新方式。64 K字節可在系統編程的FLASH存儲器。4 352(4 096+256)字節的片內RAM,可尋址64 k字節地址空間的外部數據存儲器接口。硬件實現的SPI、Sm Bus/I2C和兩個UART串行接口,5個通用的16位定時器。具有5個捕捉/比較模塊的可編程計數器/定時器陣。列片內看門狗定時器、VDD監視器和溫度傳感器,每個MCU都可在工業溫度范圍(-45~+85℃)內用2.7~3.6 V的電壓工作。端口I/O、/RST和JTAG引腳都容許5 V的輸入信號電壓。

1.2 C8051單片機軟件設計

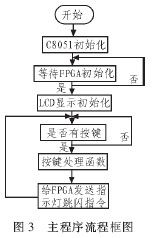

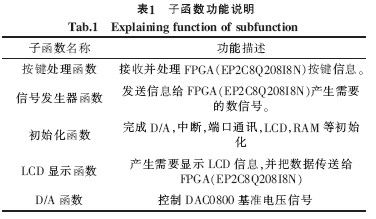

C8051單片機軟件主要包括按鍵處理函數、信號發生器控制函數、初始化函數、LCD顯示函數、D/A函數以及主函數。軟件設計的主程序流程框圖如圖3所示,子函數詳細功能如表1所示。

1.3 FPGA(EP2C8Q20818N)軟件設計

本文中主要采用Verilog HDL語言設計。主要包括片選模塊、時鐘驅動模塊、鍵盤掃描模塊、傳出信號模塊、LCD模塊、DAC0800模塊以及指示燈模塊。詳細功能如表2所示。

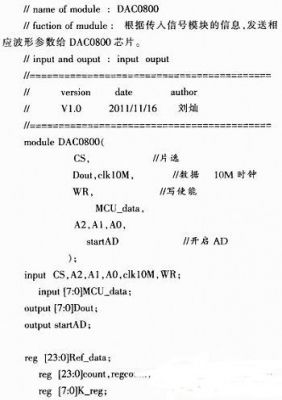

1.4 FPGA核心程序代碼,DAC0800模塊程序

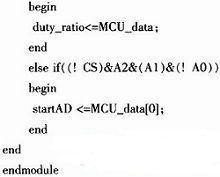

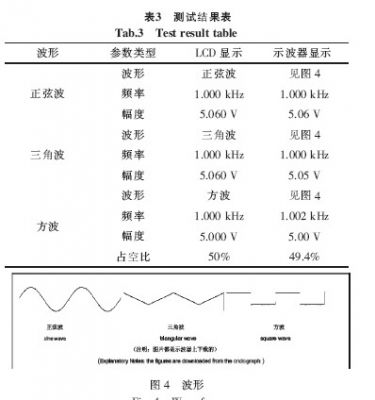

2 測試結果

3 結束語

本文中運用FPGA和51單片機結合起來制作一個信號發生器。這樣不僅能夠鍛煉學生單片機和FPGA的使用更能讓學生學習到如何將FPGA和單片機聯合通信使用。本文設計中可以對函數信精度進行升級,從而滿足不同場合的函數信號需求。本文中提倡一種將單片機和FPGA結合到一起的學習方式,可以為現代教育改革提供一個參考方向。

fpga相關文章:fpga是什么

51單片機相關文章:51單片機教程

單片機相關文章:單片機教程

單片機相關文章:單片機視頻教程

單片機相關文章:單片機工作原理

負離子發生器相關文章:負離子發生器原理 塵埃粒子計數器相關文章:塵埃粒子計數器原理

評論