基于DDS IP核及Nios II的可重構信號源設計

SOPC(System on a Programmable Chip,片上可編程系統)是Altera公司提出的一種靈活、高效的SOC解決方案。它將處理器、存儲器、I/O接口、LVDS、CDR等系統設計需要的功能模塊集成到一個可編程邏輯器件上,構建一個可編程的片上系統。它具有靈活的設計方式,軟硬件可裁減、可擴充、可升級,并具備軟硬件在系統可編程的功能。SOPC的核心器件FPGA已經發展成一種實用技術,讓系統設計者把開發新產品的時間和風險降到最小。最重要的是,具有現場可編程性的FPGA延長了產品在市場的存在時間,從而減小了被新一代同類產品淘汰的威脅。本文以全數字頻率合成技術——直接數字頻率合成技術(DDS)為理論依據,利用先進的片上可編程技術在一塊FPGA芯片上實現了DDS IP核功能,并將該DDS IP核與Nios II處理器核以及其它外設封裝到一起,做成一個片上系統,大大簡化了電路的設計難度。

本文引用地址:http://www.j9360.com/article/273564.htm1 DDS的基本原理

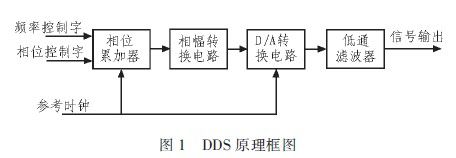

DDS(直接數字頻率合成)是把一系列數字形式的信號通過DAC轉換成模擬量形式的信號的合成技術。圖1是DDS的原理框圖。

圖中參考時鐘由一個高穩定的晶體振蕩器產生,來同步整個頻率合成器的各個組成部分。相位累加器包含一個加法器和一個相位寄存器,每來一個時鐘脈沖,加法器就將頻率控制字與相位寄存器中的數據相加。相位寄存器可以將加法器在上一個時鐘作用后產生的新相位數據反饋到加法器的輸入端,使加法器在下一個時鐘的作用下繼續將相位數據與頻率控制字相加。這樣,相位累加器在參考時鐘的作用下進行線性相位累加。當相位累加器達到上限時,就會產生一次溢出,完成一個周期性的動作,這個周期就是合成信號的一個周期,累加器的溢出頻率也就是DDS的合成信號頻率。相位控制字用來設定相位累加器初始時刻的相位值,相位累加器運行過程中并不參與加法運算。

在參考時鐘的控制下,相位累加器受頻率控制字控制輸出相位數據,用相位累加器輸出的相位數據作為相位/振幅變轉換電路的地址對其進行查找。相位/振幅轉換電路將相位累加器的相位信息映射成數字振幅信息,將數字振幅數據再經過D/A轉換器得到相應的階梯波,最后經低通濾波器對階梯波進行平滑處理,即可得到由頻率控制字決定的連續變化的輸出波形。

2 DDS IP核的設計

根據DDS的基本理論,將DDS IP核分為相位累加模塊、DDS控制模塊、波形選擇模塊、波形LPM_ROM模塊。

2.1 相位累加器模塊的設計

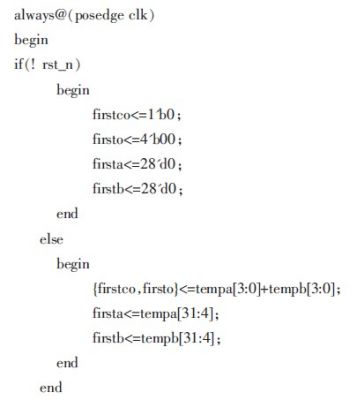

相位累加器是DDS IP核設計的關鍵,它決定著頻率的范圍和分辨率,本設計采用的32位的二進制累加器,取累加器的高十位作為查表(相幅轉換電路)的地址值。為提高系統的速率,在累加器的設計中采用了7級流水線技術。其中采用Verilog HDL描述的第一級流水線實現的關鍵代碼如下:

類似,可完成其余流水線的設計。

2.2 DDS控制模塊設計

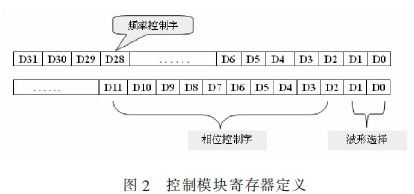

為將設計的DDS IP能夠集成到SOPC系統中,本設計在DDS IP的控制模塊定義了兩個32位的寄存器,如圖2所示。一個是頻率控制字寄存器,用來保存上位機軟件發來的頻率控制字;另一個寄存器用來保存相位控制字和波形選擇位,其中低2位D1、D0用于波形選擇,D2到D11用于保存相位控制字,其余高位保留未用。

2.3 波形存儲器ROM的設計

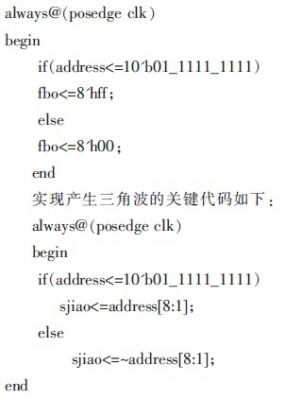

該模塊完成相位/振幅轉換電路的功能。在本設計中,要求DDS IP能輸出正弦波、方波,三角波、鋸齒波。可以用FPGA內部的LPM_ROM模塊制作4張ROM表,分別存儲4個波形的數據。實際上,由于方波和三角波是實現算法相對簡單,為了節省資源,本系統直接用Verilog HDL描述其功能。實現產生方波信號的關鍵代碼如下:

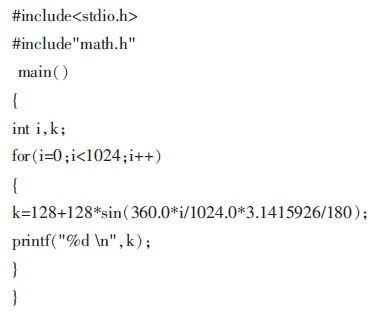

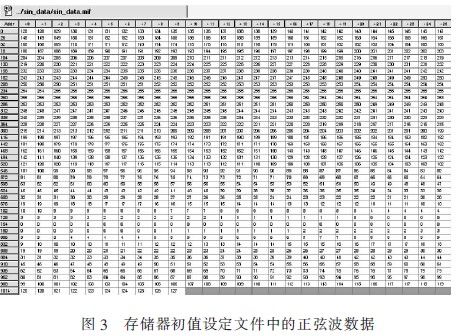

正弦波、鋸齒波的產生是利用FPGA的LPM_ROM模塊來實現。為了對ROM模塊內的數據進行加載,首先應建立相應的*.mif(Memory Initial File)文件。它可以用C語言編寫源程序,得到對應波形的數據,生成*.mif文件,如生成正弦波形數據的C語言程序如下:

然后在Quartus II里新建.mif文件,把用命令字符生成的.mif文件的內容粘貼到Quartus II里新建的存儲器初值設定(.mif)文件里面,如圖3所示。再用Quartus II軟件定制LPM_ROM,并加載剛才建立的.mif波形文件初始化ROM。

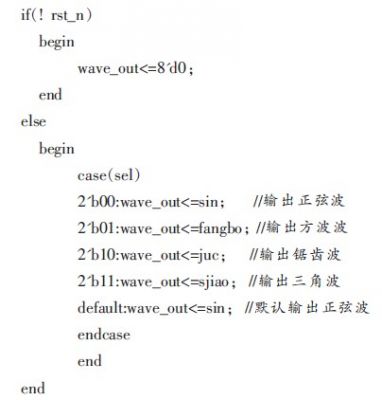

2.4 波形選擇模塊的設計

該模塊根據DDS控制模塊的輸出控制信號決定選擇哪一種波形輸出,關鍵代碼如下。

2.5 DDS頂層設計

頂層設計將前面實現的各功能模塊作為底層元件例化調用,完成整個DDS IP核設計。對DDS IP核進行驗證后,利用SOPC Builder的組件編輯器對其進行自定義組件的開發,為后續SOPC硬件系統的搭建奠定基礎。

2.6 DDS IP的仿真測試及自定義組件的生成

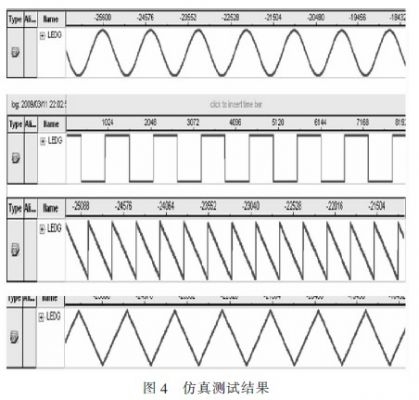

Altera公司的Quartus II軟件具有嵌入式邏輯分析儀SignalTap II,它提供了一種對器件進行實時測試的手段。SignalTapII嵌入式邏輯分析儀可以隨設計文件一起下載到目標芯片中,用以捕捉目標芯片中設計者感興趣的信號節點處的信息,而不影響芯片的正常工作。

SignalTapII將測得的樣本信號暫存于目標器件的片內RAM中,然后通過器件的JTAG端口和編程線將采得的信息傳出,送入計算機進行分析。圖4是采用SignalTapII嵌入式邏輯分析儀的仿真測試結果。

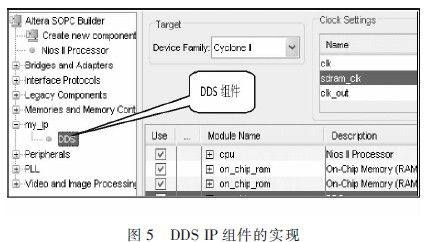

由于SOPC的開發是以組件(IP核)為基礎的,為了將前面設計的DDS IP核掛到Avalon總線上,將其封裝成為SOPCBuilder自定義的組件,如圖5所示。這樣,在SOPC硬件系統開發中,DDS IP就如同SOPC Builder里的標準組件一樣,可以被集成到具體的應用系統中。

2.7 SOPC硬件系統配置

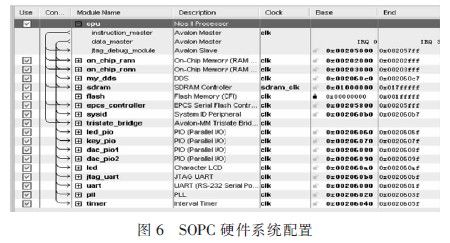

在SOPC硬件系統的開發中,除了集成前面設計的DDSIP外,還集成了諸多SOPC Builder組件庫中的標準組件,主要有Nios II CPU、UAR T、JTAG UART、定時器、Avalon三態總線橋、片上存儲器、片外存儲器、PIO、SDRAM控制器、FLASH控制器等,如圖6所示。

3 結論

論文以直接數字頻率合成技術為理論依據,開發了DDSIP核,搭建了基于SOPC技術的信號發生器硬件系統,通過改變LPM_ROM模塊中的波形數據,可以實現任意波形信號的產生。系統除了數/模轉換部分外,其它部分都是在FPGA內部完成,具有實現容易、方便,減小了PCB設計的復雜度以及開發難度,縮短了開發周期等優點,同時,系統還具有很大的伸縮性,系統集成度高,屬于SOC的范疇,符合技術發展潮流。

模擬信號相關文章:什么是模擬信號

c語言相關文章:c語言教程

低通濾波器相關文章:低通濾波器原理

存儲器相關文章:存儲器原理

評論