千兆采樣ADC確保直接RF變頻

隨著模數轉換器(ADC)的設計與架構繼續采用尺寸更小的過程節點,一種新的千兆赫ADC產品應運而生。能以千兆赫速率或更高速率進行直接RF采樣且不產生交織偽像的ADC為通信系統、儀器儀表和雷達應用的直接RF數字化帶來了全新的系統解決方案。

本文引用地址:http://www.j9360.com/article/273464.htm最先進的寬帶ADC技術可以實現直接RF采樣。就在不久前,唯一可運行在GSPS (Gsample/s)下的單芯片ADC架構是分辨率為6位或8位的Flash轉換器。這些器件能耗極高,且通常無法提供超過7位的有效位數(ENOB),這是由于Flash架構的幾何尺寸與功耗限制需要取舍。

因此,對超過1 GHz的較高動態范圍模擬輸入信號進行采樣的唯一方法,就是利用一個采樣時鐘來交錯連接多個高速ADC內核,此采樣時鐘針對每個內核都有精確的交錯相(或占空比)。模擬輸入需分割并多路復用至每一個ADC,這便為新信號噪聲進入信號鏈及降低輸入功率創造了機會。雖然此方法能為某些應用提供充分結果,但設計較復雜,并且在需要數字濾波的輸出頻域內會產生糟糕的干擾交錯偽像。

1 快速還是半速?

在快速傅里葉變換(FFT)的頻率響應中看到交錯“雜散”,其中每個內部交錯式ADC內核的輸入失調、增益、帶寬和樣本時序并非嚴格匹配。這便為系統設計人員增添了規劃復雜性,使其難以預先確定頻率內的交錯偽像,進而在數字后處理中避免或移除。

由于每一個ADC內核都是分立的,因此在量產系統的壽命期間,這些性能參數極有可能產生較大的制造失配差異。這些失配會造成輸入信號的周期性不平衡,并且交錯式ADC的輸出端會出現雜散頻率。

現在,專有ADC技術可通過先進架構與算法防止雙通道和四通道交錯式ADC內出現上述問題。使用兩個半速交錯式ADC會增加偽像,現在采用單個全速ADC可在無交錯雜散的條件下實現同樣的性能。工廠調整算法和片內校準可確保每一個ADC工作在預期的高性能標準下,避免受多個分立交錯式內核的失配差異影響。

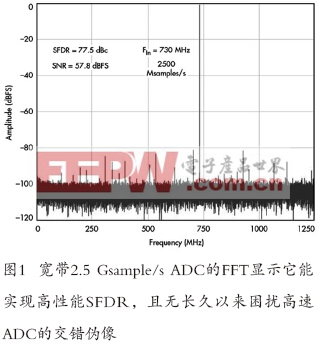

在通常頻譜純凈的FFT中觀察到雜散頻率時,會減小其他噪聲相關的載波信號的可用無雜散動態范圍(SFDR)。為了改善GSPS ADC的SFDR,除了使用交織式內核,現在又發展出新架構和算法。這樣,系統設計人員不必再使用專用ADC后處理例程來鑒別并移除干擾交錯雜散(圖1)。

2 簡化路由

10/12/14位分辨率的多個千兆采樣轉換器可在短時間內產生大量輸出數據。使用低壓差分擺幅(LVDS)數據可能需要2.5 Gsample/s、12位ADC的30條1 Gbps并行通道。就系統布局來說,針對每個ADC處理30個差分LVDS對可能會對路由和保持匹配長度提出挑戰。使用JESD204B,則僅采用6條或8條差分通道即可發送同等數據。

模數轉換器相關文章:模數轉換器工作原理

評論