基于FPGA的LZO實時無損壓縮的硬件設計

3 LZO壓縮系統集成與測試驗證

本文引用地址:http://www.j9360.com/article/273211.htm3.1 LZO壓縮系統硬件結構

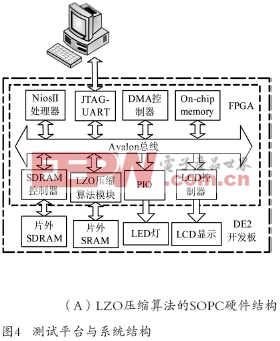

如圖4(A)為LZO壓縮系統SOPC硬件結構,內層虛線表示FPGA,虛線內的模塊有相應的代碼或硬件電路構成,外層虛線表示DE2開發板,開發板提供了相應的資源。圖中:PC機通過下載線將待壓縮的數據傳送至DE2開發板上的SDRAM,數據經壓縮后再經下載線回傳至PC機;Nios II處理器負責與用戶交互,對待壓縮數據進行管理,控制整個SOPC的正常工作;JTAG-UART用于設計過程中的軟件和硬件調試;DMA控制器用于高速數據傳輸,它將片外SDRAM中的待壓縮數據傳送到LZO壓縮算法模塊,將LZO壓縮算法模塊中被壓縮后的數據傳送到片外SDRAM中;LZO壓縮算法模塊用于對用戶傳輸過來的數據進行壓縮,它與片外SRAM進行通訊;LCD控制器用于控制LCD的顯示,LCD可顯示LZO壓縮文件開始與結束,增加用戶交互的可視性,例如顯示待壓縮文件的大小,壓縮后的文件大小等;PIO控制LED指示燈的亮與滅,LED燈可用于指示LZO壓縮文件開始與結束,增加用戶交互的可視性;On-chip memory用于存儲系統啟動時的軟硬件配置等信息;SDRAM控制器用于控制SDRAM與系統數據的交換;SDRAM用于存儲指令和數據;SRAM用于存儲LZO壓縮算法過程中產生的壓縮信息,在硬件設計中扮演字典的角色,采用片外SRAM的原因是考慮到FPGA片內資源可能不夠使用;以上所有涉及到的模塊均采用Avalon總線規范進行數據通信,它們共同掛載到數據總線上,Avalon總線具有自身的仲裁結構、地址分析等功能,易于用戶集成開發。

3.2 開發板簡介

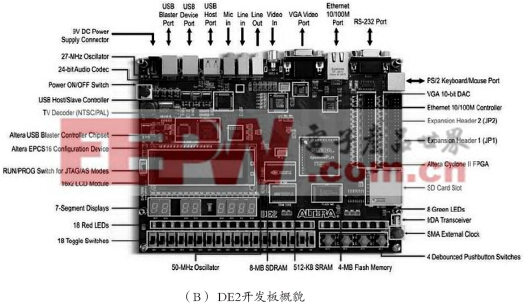

測試與驗證平臺如圖4(B)所示的DE2開發板,該開發板上的核心芯片為Altera公司的Cyclone II EP2C35 FPGA。選擇該開發板作為測試平臺主要基于以下考慮:擁有足夠的片外存儲資源(SDRAM 8MB、SRAM 512KB);擁有較豐富的片上邏輯資源(35K LEs);擁有豐富的可用于調試的外設(LCD、7-segment-displays);支持 Nios II嵌入式軟核;成本較低。

3.3 測試結果及對比

針對LZO壓縮算法模塊和集成后的系統進行板級測試,一方面驗證算法模塊及集成后的系統的功能正確性,另一方面測試分析算法模塊及集成后系統的性能。測試內容包括:數據壓縮率(壓縮后的文件大小/壓縮前的文件大小),數據壓縮速率(單個周期內處理的字節數)。

通過圖5(A)可知,壓縮率提升最大的是1.pdf文件,提升最小的是7.mp3文件(音頻文件已經采用音頻壓縮算法壓縮過了),除去最大值和最小值后取平均值,則壓縮率提升為1.37%;通過圖5(B)不難發現,壓縮速率提升最快的為2.txt文件,提升最慢的為10.dll文件,除去最大值和最小值后取平均值,則壓縮速率提升為4.81倍。

fpga相關文章:fpga是什么

網線測試儀相關文章:網線測試儀原理

評論