ISE時序約束筆記6——Timing Groups and OFFSET Constraints

回顧全局OFFSET約束

本文引用地址:http://www.j9360.com/article/270620.htm在時鐘行中使用Pad-to-Setup和Clock-to-Pad列為所有出于該時鐘域的I/O路徑指定OFFSETs。

為大多數(shù)I/O路徑進(jìn)行約束的最簡單方法——然而,這將會導(dǎo)致一個過約束的設(shè)計(jì)。

指定管腳的OFFSET約束

使用Pad-to-Setup和Clock-to-Pad列為每個I/O路徑指定OFFSETs。

這種約束方法適用于只有少數(shù)管腳需要不同的時序約束。

更常用的方法是:

1. 為Pads生成Groups

2. 對生成的指定Groups進(jìn)行OFFSET IN/OUT約束

雙沿時鐘的OFFSET約束

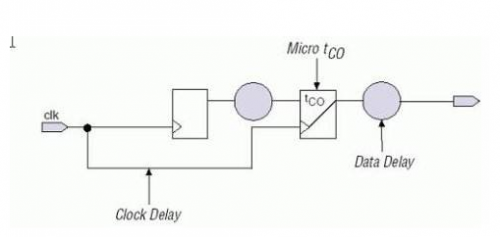

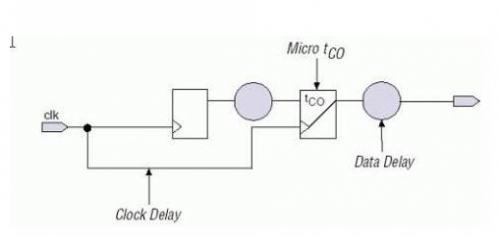

OFFSET約束指明了FPGA管腳的輸入數(shù)據(jù)和初始時鐘之間的關(guān)系。

初始時鐘沿在周期約束定義中出現(xiàn)關(guān)鍵詞“高”和“低”。

——高:初始時鐘上升沿(默認(rèn)),即上升沿鎖存數(shù)據(jù)

——低:初始時鐘下降沿

如果所有的I/O都由時鐘的一個沿控制,那么你可以使用這個關(guān)鍵字高或低進(jìn)行周期約束。

如果兩個沿都用到,你就必須進(jìn)行兩個OFFSET的約束。

——每個OFFSET對應(yīng)一個時鐘沿

——DDR寄存器也是這樣使用的一個例子

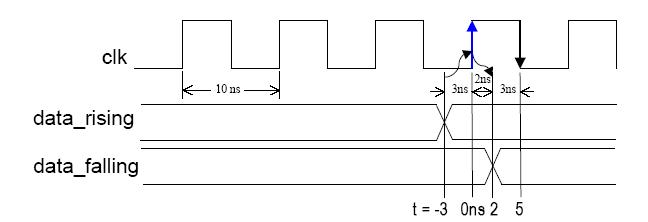

雙沿時鐘的OFFSET IN約束

輸入數(shù)據(jù)在上升沿或者下降沿之前3ns有效——周期約束為10ns,初始上升沿,占空比為50%。

為每個時鐘沿生成一個時鐘Groups

——輸入時鐘的上升沿,OFFSET = IN 3ns BEFORE CLK;

——輸入時鐘的下降沿,OFFSET = IN -2ns BEFORE CLK;(在初始時鐘的上升沿后2ns = 時鐘下降沿前3ns)

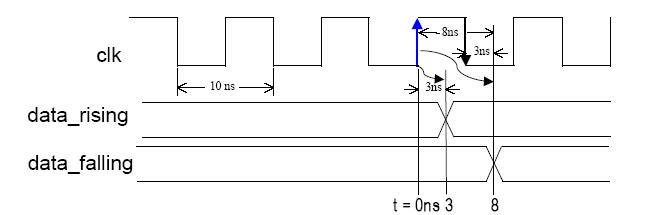

雙沿時鐘的OFFSET OUT約束

輸出數(shù)據(jù)必須在時鐘的上升沿或者下降沿后3ns內(nèi)有效——周期約束為10ns,初始上升沿,占空比為50%。

為每個時鐘沿生成一個時鐘Groups

——輸入時鐘的上升沿,OFFSET = OUT 3ns AFTER CLK;

——輸入時鐘的下降沿,OFFSET = OUT 8ns AFTER CLK;(在初始時鐘的上升沿后8ns = 時鐘下降沿后3ns)

問題思考

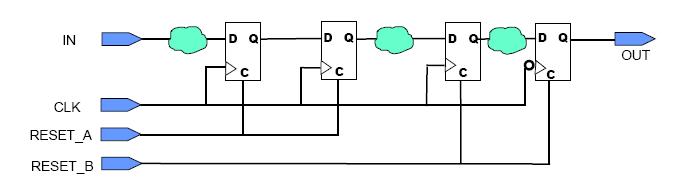

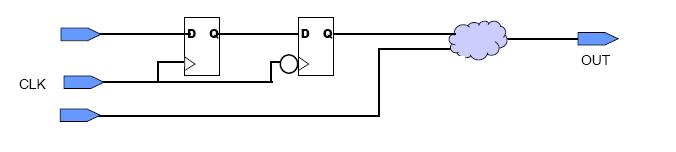

特定路徑時序約束如何改善了設(shè)計(jì)性能?

你如何約束這個設(shè)計(jì)使其內(nèi)部時鐘頻率達(dá)到100 MHz?

輸入(數(shù)據(jù))將在時鐘CLK的上升沿到達(dá)前3ns內(nèi)有效。輸出數(shù)據(jù)必須在時鐘CLK的下降沿后4ns內(nèi)穩(wěn)定下來。寫出合適的OFFSET約束?

問題解答

特定路徑時序約束如何改善了設(shè)計(jì)性能?

——它使得執(zhí)行工具更加靈活的達(dá)到你的時序要求。

你如何約束這個設(shè)計(jì)使其內(nèi)部時鐘頻率達(dá)到100 MHz?

——給時鐘信號CLK施加一個10ns的全局周期約束。

寫出合適的OFFSET約束?

——OFFSET = IN 3 ns BEFORE CLK; OFFSET = OUT 4 ns AFTER CLK;

評論