達芬奇數字媒體片上系統的架構和Linux啟動過程

達芬奇(DaVinci)數字媒體技術平臺TMS320DM6446/3采用了ARM+DSP雙核的架構,本文從芯片的硬件結構入手介紹達芬奇DMSoC硬件部分及Linux OS的啟動過程。

本文引用地址:http://www.j9360.com/article/269184.htmlinux操作系統文章專題:linux操作系統詳解(linux不再難懂)

達芬奇DMSoC硬件概述

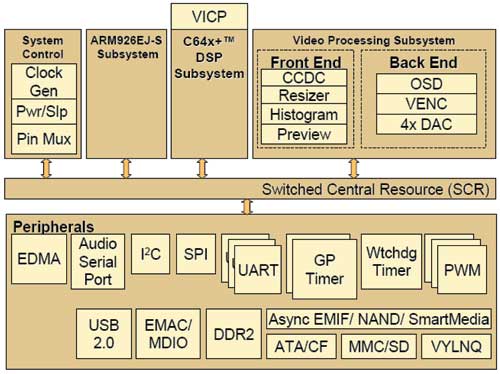

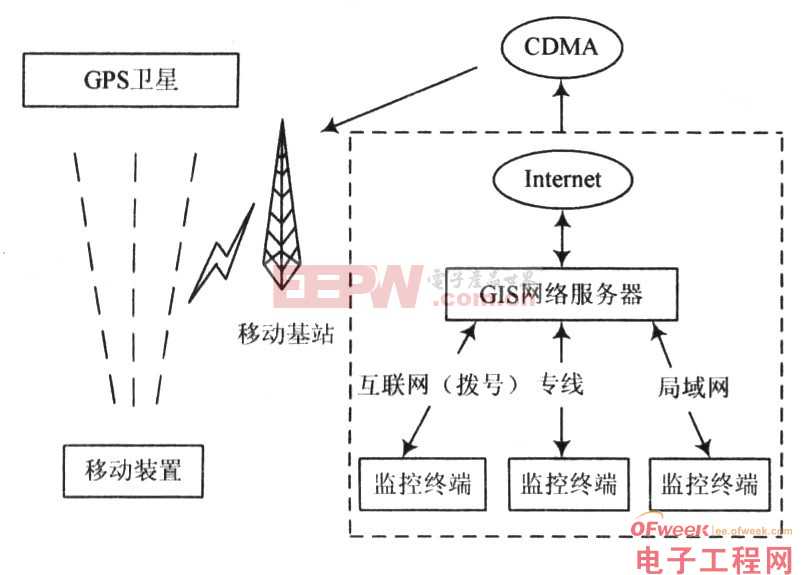

如圖1所示,達芬奇數字媒體片上系統(DMSoC)提供:兩個內核(ARM+DSP);視頻處理子系統(VPSS);多種Boot模式(NOR Flash/NAND Flash/UART0 Boot Mode);兩個電源域;多個時鐘樹;多個引腳獨立或復用的外設。

圖1 DM6446功能結構框圖

● ARM-DSP集成

對于雙核的達芬奇架構,大家最關心的就是兩個核之間的資源分配、通信方式及如何高效地實現資源共享各盡其能。ARM獨享(DSP不可用)的外設有:UART0/1/2,I2C,看門狗定時器,PWM0/1/2,ARM中斷控制器,USB2.0,ATA/CF,SPI,GPIO,VPSS,EMAC/MDIO,EMIFA CONTROL,VLYNQ,MMC/SD。DSP獨享(ARM不可用)的外設有:DSP中斷控制器,VICP。ARM和DSP共享的外設有:EDMA,Timer0/1,Power & Sleep Controller,ASP和EMIFA Data。

圖2 ARM-DSP集成結構

如圖2所示,可以很清楚地看到ARM可以訪問DSP片內存儲器(L2RAM和L1P/D);DSP可以訪問ARM片內存儲器;ARM和DSP共享DDR2和AEMIF。因此,通常情況下ARM只需傳遞需要處理的數據地址指針給DSP,而無須大塊的數據搬移。ARM和DSP之間的通信可以通過相互中斷實現。ARM可以中斷DSP(通過4個通用中斷和1個不可屏蔽中斷);DSP可以通過2個通用中斷來中斷ARM。ARM控制DSP的電源、時鐘、復位和引導。

● DMSoC存儲器映射

達芬奇DMSoC多個片上存儲器和兩個處理器及不同的子系統相關。為了簡化軟件開發,DMSoC中所有的存儲器統一編址,如表1所示。

linux相關文章:linux教程

存儲器相關文章:存儲器原理

數字濾波器相關文章:數字濾波器原理

評論