基于CPLD技術的CMOS圖像傳感器高速采集系統

在當前圖像傳感器市場,CMOS傳感器以其低廉的價格得到越來越多消費者的青睞。在目前的應用中,多數采用軟件進行數據的讀取,但是這樣無疑會浪費指令周期,并且對于高速器件,采用軟件讀取在程序設計上、在時間配合上有一定的難度。因此,為了采集數據量大的圖像信號,本文設計一個以CPLD為核心的圖像采集系統,實現了對OV7110CMOS圖像傳感器的高速讀取,其讀取速率可達8 Mb/s。

本文引用地址:http://www.j9360.com/article/268283.htm1、硬件電路方案

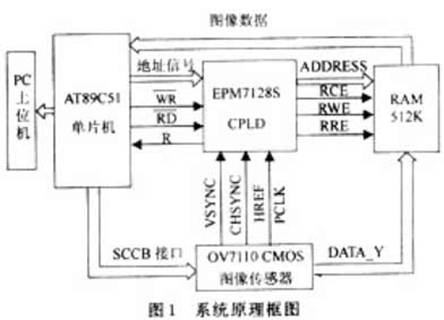

圖1為基于CPLD的OV7110CMOS圖像傳感器的高速數據采集系統原理框圖,他主要由2個部分組成:OV7110的參數設置電路和圖像采樣電路。

1.1 OV7110的參數設置電路

系統在上電后需要對CMOS采樣芯片進行初始化,以 確定其工作模式、窗口大小、掃描方式、輸出數據格式等。這些參數是通過OV7110芯片上的SCCB接口進行的。

SCCB是OmnVision公司開發的一種雙向三線的同步串行總線,引線接口有使能線SCCB_E,時鐘線SIO_C,數據線SIO_D。其中SCCB_E低電平有效,如果將其接地,那么SIO_C,SIO_D的工作方式十分類似于I2C總線。OV7110工作模式、窗口大小、掃描方式、輸出數據格式均可以通過相應的寄存器來設置,本系統把AT89C51作為主設備(MasterDevice),OV7110作為從設備(Slave Device),采用AT89C51的P1.2和P1.3口用軟件模擬SCCB總線,把其參數寫入其內部對應的寄存器。與I2C總線一樣,在SCCB總線中主設備發送一個字節后,從設備需要將數據線SIO_D拉低作為應答信號(ACK)返回給主設備,才能表示發送成功。值得注意的是由于CMOS器件所能承受的灌電流很低,所以接至時鐘線SIO_C、數據線SIO_D的上拉電阻阻值應在3~5 kΩ之間,并且對于主設備AT89C51發送參數完畢后,需立即釋放數據線SIO_D以保證其處于懸空狀態,即AT89C51在送完一個字節后立即執行一條指令,使數據線SIO_D發出讀取信號的操作。

1.2 圖像采樣電路

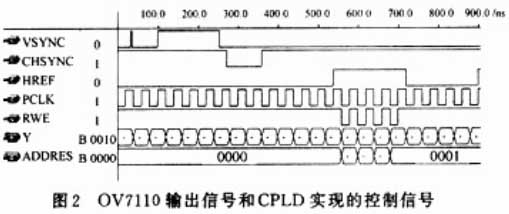

本系統設置的工作模式為黑白,分辨率取到了最大640×480。CMOS芯片的數據輸出波形如圖2所示(為了便于分析,該圖只是示意圖)。圖中VSYNC為垂直場同步信號,其下降沿表示一幀圖像的開始。HSYNC為水平行同步信號,其上升沿表示一行信號開始。HREF為水平窗素時鐘信號,即數據輸出同步時鐘信號,其下降沿更新數據,上升沿數據是穩定時期,可以讀取數據,其數據按行輸出。Y為圖像灰度數據。

傳感器相關文章:傳感器工作原理

風速傳感器相關文章:風速傳感器原理 上拉電阻相關文章:上拉電阻原理

評論