基于32位NiosⅡ軟核系統的電能質量監測系統設計

在電力系統中,要實現對電能質量各項參數的實時監測和記錄,必須對電能進行高速的采集和處理,尤其是針對電能質量的各次諧波的分析和運算,系統要完成大量運算處理工作,同時系統還要實現和外部系統的通信、控制、人機接口等功能。而電能質量監測系統大多以微控制器或(與)DSP為核心的軟硬件平臺結構以及相應的設計開發模式,存在著處理能力不足、可靠性差、更新換代困難等弊端。本文將SoPC技術應用到電力領域,在FPGA中嵌入了32位NiosⅡ軟核系統。可實現對電能信號的采集、處理、存儲與顯示等功能,實現了實時系統的要求。

本文引用地址:http://www.j9360.com/article/268261.htm1 系統概述

1.1 電能質量檢測系統的基本原理

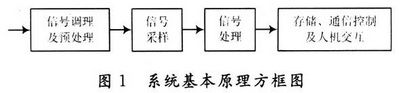

電能質量監測主要是對電能質量各參數進行實時監測和記錄,其功能流程為:把電網中的電壓、電流經過PT、CT變成-5~+5 V的電壓信號、1~2 mA的電流信號,預處理后進行采樣,對采樣值進行數據處理,處理結果可以存儲在數據存儲單元,也可以通過通信模塊與計算機終端進行通信,根據需要控制且查看處理結果。其系統基本原理方框圖如圖1所示。

1.2 算法介紹

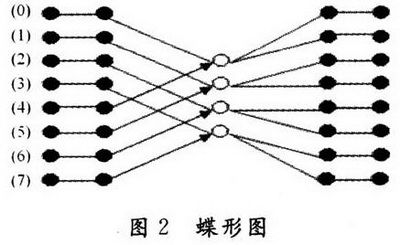

本文在處理諧波數據時,采用基2的DIT方式的FFT算法。傳統的基2算法的蝶形圖中輸入采用的是按碼位顛倒的順序排放的,輸出是自然順序。同一位置不同級的蝶形的輸入數據的位置不固定,難以實現循環控制,用FPGA編程時難以并行實現,通過對傳統的基2蝶形圖分析,調整其旋轉因子的位置,使得各級蝶形圖一致,如圖2所示,可以實現循環控制。

這種結構的輸入是順序的,而輸出是位反碼的,每級的旋轉因子都是放在FPGA的片內ROM里的。調整后的旋轉因子的尋址有一定規律,對于N點的FFT(N=2k,K為級數),旋轉因子有,…,,共N/2個,將他們按位碼倒序的形式排成一個含有N/2個元素的數組,記為:,,則第i級(i=O.1,2,…,K-1)的旋轉因子排列順序是W(O),W(1),W(2),…,W(2i)重復2k-i-l次得到的。其特點是每級的輸入、輸出數據的順序是不變的,因此每級幾何結構是固定的。用這種結構尋址方便,易于用FPGA編程,實現內部并行的FFT硬件結構,從而明顯加快FFT的運算速度。

2 電能質量檢測系統硬件設計

2.1 A/D轉換器

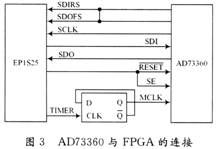

根據實測數據,如果采用12位分辨率的A/D轉換芯片,對15次諧波而言至少會引起1.67%的誤差,而在實際諧波測量中一般測到30次或更多次諧波,因此現場監測單元中A/D轉換器的分辨率應保證為14位或14位以上。本文采用AD73360作為采樣系統的模數轉換芯片。它的六路輸入通道可被分為三對,以分別對應電力系統中的三相。該芯片可以8 kHz,16 kHz,32 kHz,64 kHz的采樣速率同時進行六通道的信號采樣。AD73360可滿足裝置對高速采樣的要求。AD73360與FPGA的連接如圖3所示。

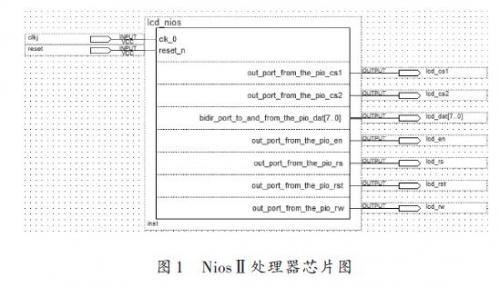

2.2 NiosⅡ軟核處理器

基于32位RISC嵌入式軟核NiosⅡ的SoPC,有著其他SoPC(如基于FPGA嵌入式IP硬核SoPC)不可比擬的優勢。采用NiosⅡ軟核處理器,用戶將不會局限于一般的處理器技術而是根據自己的標準裁剪和定制處理器,按照需要選擇合適的外設、存儲器和接口,輕松集成自己專有的功能,比如DSP、用戶邏輯等。這非常有利于設計高次諧波這種計算量大且控制邏輯復雜的系統。

為了滿足今后的性能要求,該電能質量監測系統應能隨時被改進升級。可以加入多個NiosⅡCPU、定制指令集、硬件加速器等,以達到更好的性能目標。還可以通過Avalon交換架構調整系統性能,該架構支持多種并行數據通道可實現大吞吐量的應用。

2.3 硬件系統平臺設計

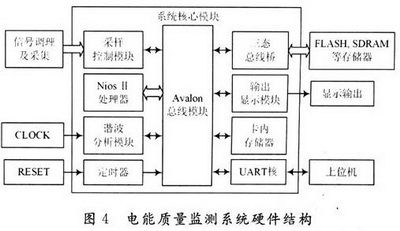

圖4是整個系統的硬件結構框圖。系統組成主要包括:

pid控制相關文章:pid控制原理

pid控制器相關文章:pid控制器原理

評論