基于NiosⅡ的1553B總線通訊模塊設計與開發

自2005年9月LXI總線推出以來,已經顯示出其組建測試系統的眾多優點。基于LXI總線組建測試系統具有易于使用、靈活性高、模塊化和可擴縮性、實現更快的系統吞吐率、可分布式應用、長壽命、低成本、通過IEEE1588時鐘同步、機架空間小、合成儀器等諸多優點。

本文引用地址:http://www.j9360.com/article/268250.htm1553B總線的全名為“時分制指令/響應式多路傳輸數據總線”,國內多型戰斗機、軍艦等武器平臺都采用其作為傳輸總線。因此研制基于LXI總線的1553B通訊模塊,不僅能滿足多型武器裝備對1553B總線的測試需求,也對LXI總線在國內的研究和應用有推動作用。

1 模塊總體方案

模塊基本設計指標為:滿足LXI規范C類儀器標準;支持DHCP、自動配置IP地址和手動配置IP地址;支持ICMP協議、TCP/IP協議和UDP協議;同步采用網絡命令方式;能完成1553B在BC模式下的所有功能。

根據指標要求采用基于SOPC的32位處理器+實時多任務操作系統(Real Time Operation System,RTOS)總體方案,在一塊FPGA芯片上集成了控制器和邏輯單元,既降低了開發的難度、減少了模塊體積,也易于以后的升級。32位處理器有足夠的資源可以擴充利用,RAM和ROM可以做的足夠大,整個TCP/IP協議族可以做到系統里面去,甚至可以嵌入一個帶TCP/IP協議族的操作系統。

2 基于SOPC的硬件設計與開發

片上可編程系統(System on a Programmable Chip,SOPC)將處理器、存儲器、I/O口、LVDS和CDR等系統設計需要的功能模塊集成到一個PLD器件上構建成一個可編程的片上系統,是一種靈活高效的SOC解決方案。SOPC結合了SOC和可編程邏輯器件各自的優點,具有靈活的設計方式、可剪裁、可擴充、可升級,并具備軟硬件在系統可編程的功能,成為SOC設計的新趨勢。

2.1 模塊硬件架構

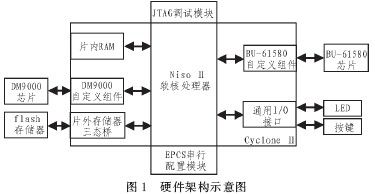

模塊硬件主要由NiosII軟核處理器、以太網組件、1553B總線組件、存儲器、片內RAM、通用I/O接口和調試配置模塊7部分組成,架構示意如圖1所示。

1)NiosII軟核處理器:模塊的CPU,負責系統工作調度。在其內部移植了μC/OSII實時操作系統和LwIP協議;它接受客戶端通過以太網發送過來的請求,經解析后回復Web界面或控制1553B功能接口;2)以太網組件(DM9000A):完成對以太網控制器的操作,將網絡上的數據經以太網控制器送到網際層,由NioslI軟核處理器內的LwIP協議處理;或者將網際層送來的數據經以太網接口發送出去:3)1553B總線組件(BU-61580):受NiosllI軟核處理器控制,完成在BC模式下各類消息和命令的發送及狀態的讀取;4)Flash存儲器:主要用來存儲模塊的一些固定參數和靜態Web界面;5)片內RAM:RAM是在FPGA剩余邏輯中用Quartusll內所帶的MegaWizard管理器生成的,這樣就不需要外加RAM芯片。片內RAM主要是用來存儲程序運行過程中所接收和產生的一些數據;6)通用I/O接口:用來完成對LED或按鍵的控制;7)JTAG調試模塊和EPCS配置模塊:J1TAG模塊用來完成對程序的調試工作。配置是對FPGA的內容進行編程的過程,每次上電后都需要配置,EPCS配置模塊允許NioslI訪問EPCS串行配置器件。

具體開發主要有3部分工作:1)NiosII軟核處理器及其外設的設計。2)自定義宏功能模塊RAM的開發,這部分工作在QuartuslI軟件中完成;3)應用軟件程序的編寫,在NiosIIIDE軟件開發環境中完成。

2.2 模塊硬件設計

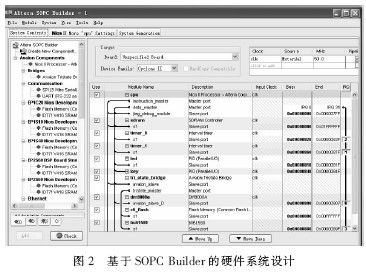

SOPC Builder是Altera公司為用戶自定義系統而開發的工具。用戶使用SOPC Builder可以將IP核、存儲器、接口、微處理器和自定義組件等復雜系統組件簡單又快速的集成到Ahera高密度FPGA芯片上。按照模塊硬件系統的要求,借助SOPC Builder生成的模塊硬件結構,包括:32位標準NiosII軟核處理器:cpu;JTAG調試接口:jtag-debug-module;外部SDRAM存儲器接口:sdram;Avalon三態橋:tri_state_brid ge;EPCS串行閃存控制器:EPCS_controller;外部FLASH存儲器接口:cfi_flash;定時/計數器:time0/timel;以太網接口:dm9000a;1553B接口:bu61580;LED接口:led;64KRAM接口:RAM;按鍵接口:key;系統識別模塊:sysid。

2.3 宏功能模塊RAM生成

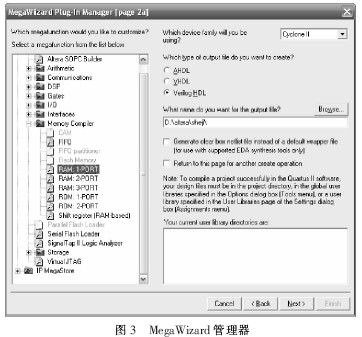

CycloneII器件內部的RAM塊只有M4K一種,可用來實現真正的雙端口、簡單雙端口和單端口的RAM,可以支持移位寄存器和ROM方式。用QuartusII內所帶的MegaWizard管理器來生成RAM,首先運行MegaWizard管理器選擇“創建一個新的宏功能”,在出現的對話框內選擇Insta lled Plug-Ins下的memory compiler下的RAM:1-PORT,如圖3所示。

在接下來的各頁中選擇如下參數:數據線寬度16位;存儲64個字;自動單時鐘驅動;選擇生成*.v,*.bsf,*_inst.v,*_bb.v,*_waveforms.html 5個文件。其他參數默認即可。

tcp/ip相關文章:tcp/ip是什么

通信相關文章:通信原理

存儲器相關文章:存儲器原理

評論