基于FPGA及NiosII軟核處理器的TFT-LCD接口設計

1 引言

本文引用地址:http://www.j9360.com/article/266854.htm隨著電子技術的飛速發展,TFT-LCD作為在亮度、對比度、功耗、壽命、體積和重量等綜合性能上全面趕上和超過 CRT的顯示器件,被廣泛用于各種儀器儀表、電子設備及控制領域中。與之相關的顯示控制技術也呈現出越來越多的方式。本文以 640*480的數字輸入的 TFT_LCD顯示屏為例,介紹了一種基于 NiosII軟核處理器實現對 TFT-LCD接口的方法。解決了通常情況下必須使用LCD 控制專用芯片才能解決 LCD顯示的問題。

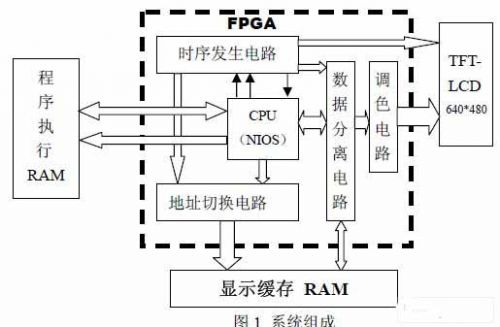

2 系統組成

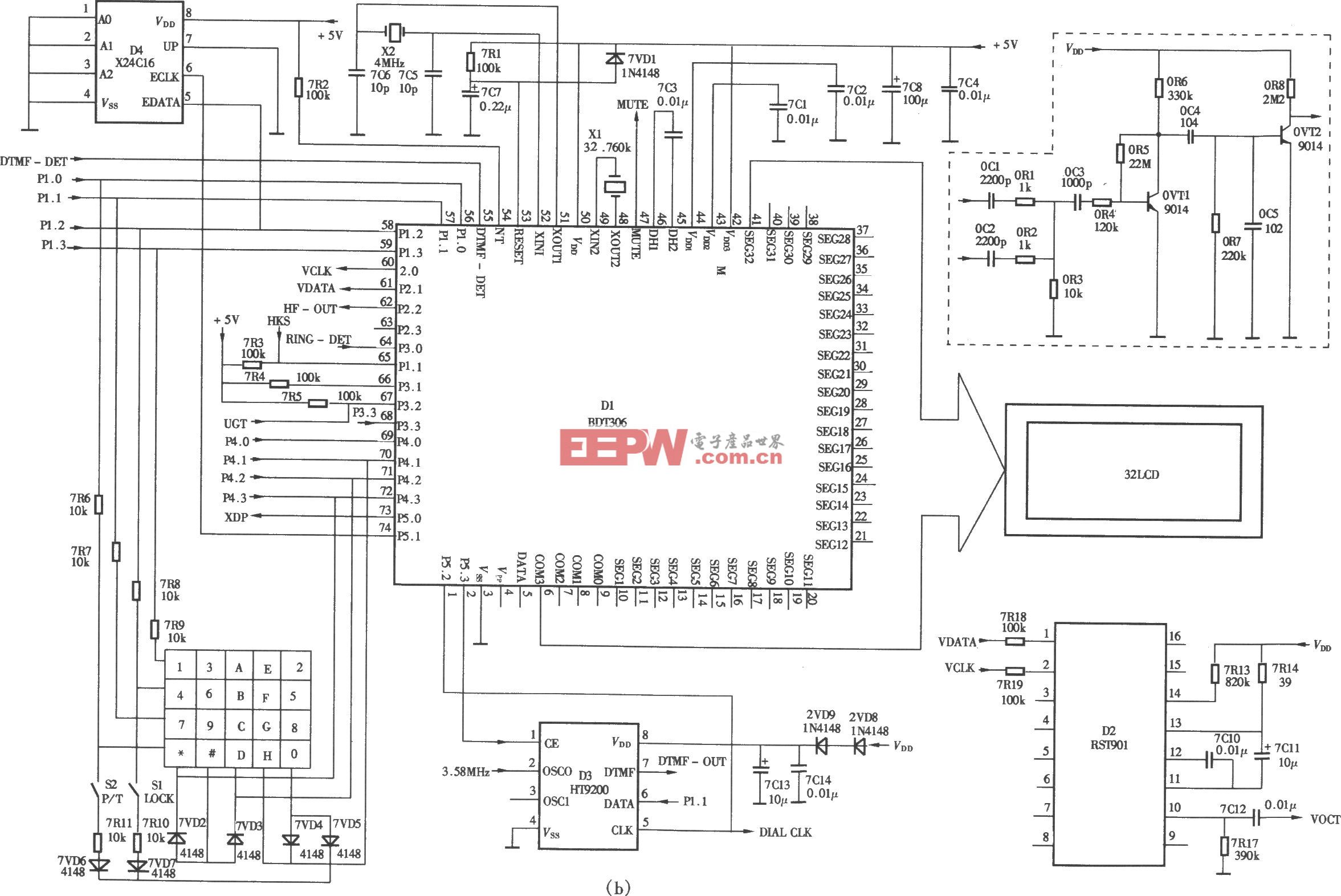

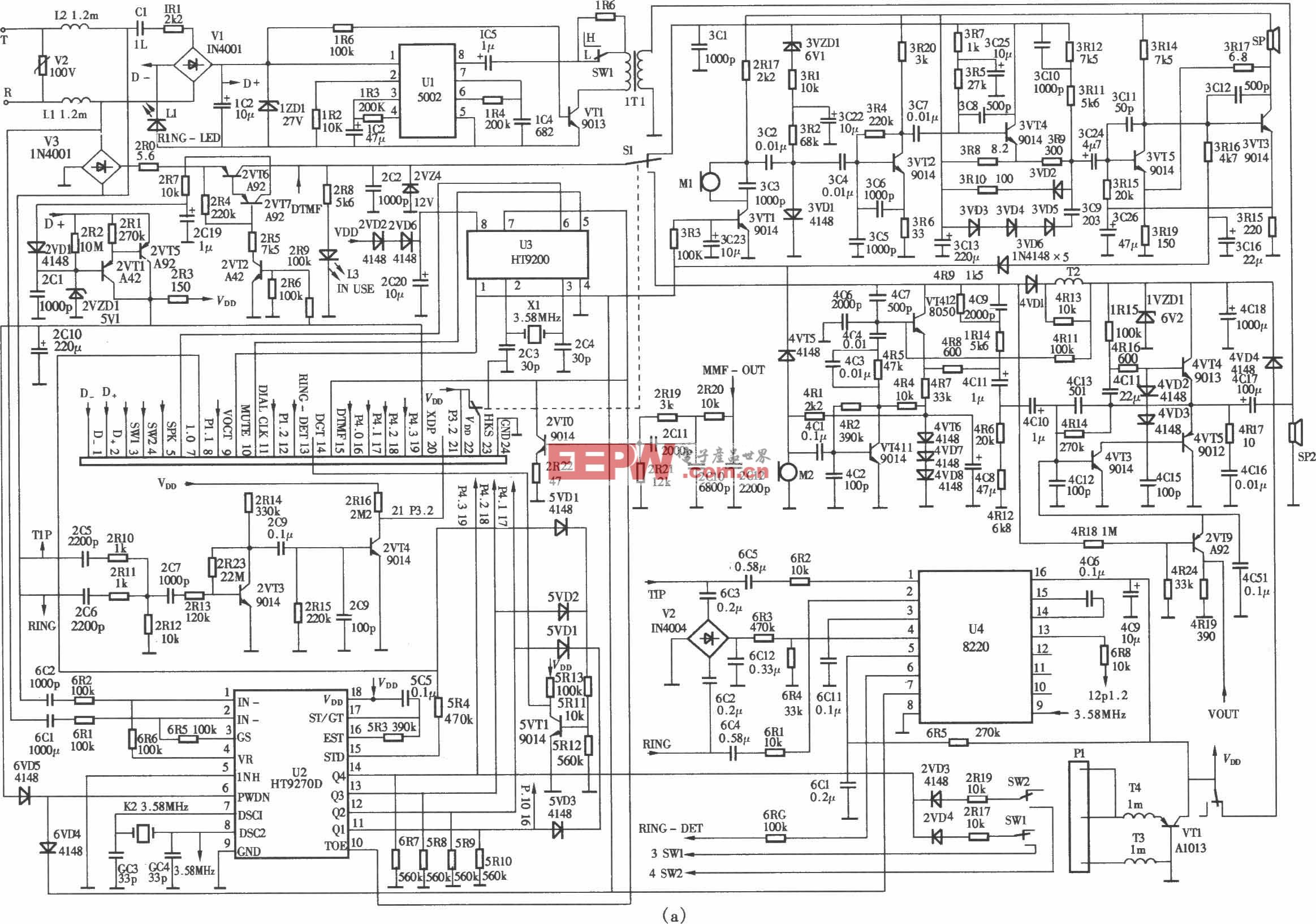

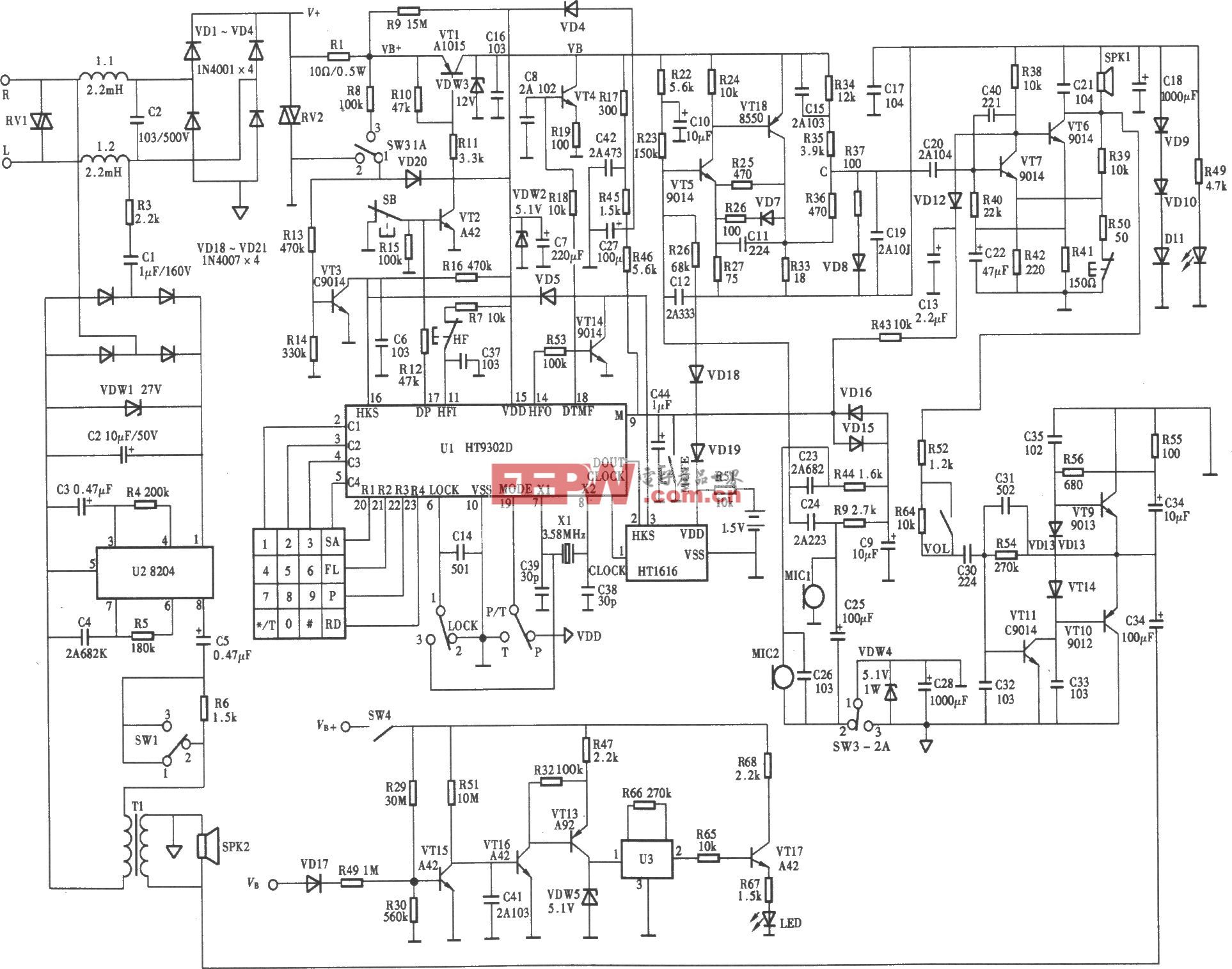

系統框如圖 1所示。系統是由 FPGA、顯示緩存 RAM、程序執行 RAM及 TFT-LCD組成。 FPGA(用虛線圍成)選用的是 ALTER的 EP1C6,RAM采用的是 IDT的 IDT71V547,LCD為 640*480的彩色 TFT-LCD屏。在 FPGA內部是由時序發生、 地址切換、數據分離、調色電路及嵌入式 CPU(NIOS內核)五部分組成。

3各器件的功能

3.1顯示緩存 RAM

采用 IDT公司的 IDT71V547 128K X 36bit的 SRAM芯片,工作電壓為 3.3V [1]。該芯片作為顯示緩存,TFT_LCD讀取顯示緩存 RAM中的數據并將其在 TFT_LCD上顯示。嵌入式 CPU(NIOSⅡ)對顯示緩存 RAM的改寫就相當于對 TFT_LCD顯示內容的改寫。

3.2 FPGA

本文 FPGA選用的是 ALTERA公司的 Cyclone 系列中 EP1C6Q240。

3.2.1 時序發生電路

首先由外部輸入一相當的頻率時鐘,通過 FPGA內部的鎖相環電路(PLL)生成 100MHz的時鐘信號。系統對 100MHz時鐘計數生成 50MHz的時鐘給嵌入式 CPU(NIOSⅡ)作為嵌入式 CPU的工作主頻,同時生成 TFT_LCD所須的場同步時鐘、行同步時鐘、顯示使能時鐘和 25MHz的 TFT_LCD主時鐘;生成地址切換控制信號、數據分離控制信號,由嵌入式 CPU輸出的讀寫信號產生顯示緩存 RAM的讀寫信號。

3.2.2調色電路

由于文中是以 256色的電路為例,所以,調色電路是將 8位數據譯碼成 3*6位的三基色數據,調色電路也可以是 ROM型或 RAM型。如果作成 RAM型,可以依據嵌入式 CPU需要顯示的圖象相應修改調色電路,可顯示更豐富的色彩。

3.2.3地址切換、數據分離

此部分電路的作用是:在嵌入式 CPU操作顯示緩存 RAM時將地址、數據線切換到嵌入式 CPU,在 TFT-LCD讀顯示緩存 RAM時將地址、數據線切換到 TFT_LCD。

3.3 TFT-LCD

SHARP公司生產的 *英寸液晶顯示屏LQ064V3DG01是較為常用的 TFT-LCD液晶顯示屏,它的分辨率為 640×480×RGB[2],具有功耗低、體積小、重量輕、超薄等特點,同時該顯示屏是一片真彩顯示屏,并屬于透光型的 TFT、其亮度高、視角寬、背光燈的壽命也很長,并且采用的是 AG涂層和 260K的彩色顯示。可廣泛應用于各種儀器儀表及各種視頻顯示的場合。

LCD顯示屏相關文章:lcd顯示屏原理

fpga相關文章:fpga是什么

led顯示器相關文章:led顯示器原理

lcd相關文章:lcd原理 鎖相環相關文章:鎖相環原理

評論