基于FPGA的電力諧波檢測設計

2 系統硬件電路設計

本文引用地址:http://www.j9360.com/article/266584.htm如圖4所示,系統硬件由兩大部分組成,分別是虛線框內的采樣電路部分和開發板部分[6-7]。本文采用的Spartan-3A DSP 入門級開發板是Xilinx公司出品的基于Spartan-3A DSP FPGA設計的一個開發平臺。采樣電路實現對三相電壓、電流的整周期同步采樣,其設計尺寸與Spartan-3A DSP開發板相同,通過EXP接口實現與開發板的通信。它包括:電壓、電流互感器、調理電路、低通濾波電路、鎖相倍頻電路、AD轉換器及電平轉換電路。

3 硬件聯合仿真與結果分析

3.1 硬件聯合仿真

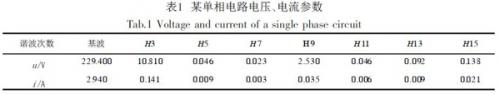

由于實驗條件所限,本文采用的是單相220V的市電為檢測對象。接入額定電壓220V,標稱功率800W的電加熱器為負載。首先用FLUKE434型電能 質量分析儀檢測出該負載上的電壓、電流的各次諧波參數,如表1所列,其電壓總諧波畸變率THDV=4.9%,電流總諧波畸變率THDI=4.8%。

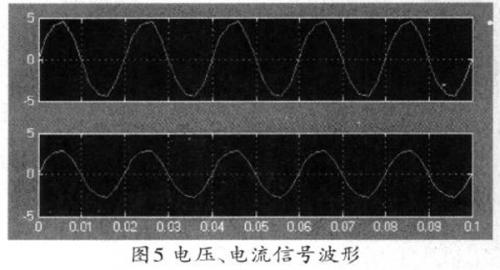

經采樣后得到的數字信號量在0~5V之間,依照給定參數分別乘系數J、K,利用Simulink中模塊生成一組表征電壓、電流的數字信號作為系統的輸入信號。如圖5所示。

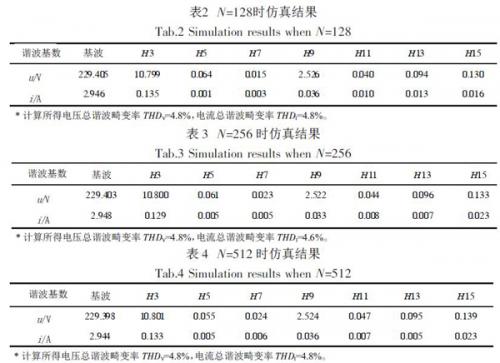

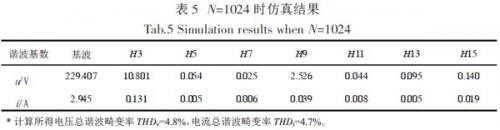

將FFT模塊中的采樣點數分別設置成為128、256、512、1024,并設置相應的采樣頻率,然后運行硬件聯合仿真模型;將計算結果再乘系數1/J、1/K,得到表2~表5所示結果。

3.2 仿真結果分析

由各表中可以看出,計算出的幅值以及根據幅值計算所得總諧波畸變率的誤差都比較小。隨著采樣點數的增加,計算所得基波和較低次數的諧波幅值的誤差和總諧波 畸變率的誤差并沒有明顯減小,而次數較高的諧波誤差減小較明顯。究其原因,N點FFT計算可以分解出0~N/2-1次諧波,N=128時就可以分解出63 次以內的諧波了。而對于次數較高的諧波,采樣點數的增加對其幅值誤差的改善還是比較明顯的。硬件實現時,在計算精度滿足要求的情況下,考慮到實時性的要 求,可選用256點FFT進行計算。

此外,計算所得相位出現了很大的偏差;原本設想通過改變待測信號參數,分析仿真結果來推導出相位偏差的規律,但是隨著數值的改變,相位偏差規律并不 明顯,并未達到預期目的。然而,在改變信號參數的分析過程中發現,相位的改變對諧波幅值和總諧波畸變率的計算并沒有太大影響,計算精度基本滿足要求。因 此,實際硬件實現時,舍棄掉相位計算,只計算出各次諧波的幅值及總諧波畸變率。

4 結束語

本文提出了一種采用基于Xilinx FPGA 實現FFT算法的電壓、電流諧波檢測的模塊化的設計方法。使用System Generator設計了諧波檢測的模型及前端采樣電路,并以Spartan-3A DSP開發板為平臺進行了硬件聯合仿真驗證。

互感器相關文章:互感器原理

fpga相關文章:fpga是什么

混頻器相關文章:混頻器原理

評論