FPGA研發之道(18)-設計不是湊波形(八)總線(上)

如果設計中有多個模塊,每個模塊內部有許多寄存器或者存儲塊需要配置或者提供讀出那么實現方式有多種,主要如下:

本文引用地址:http://www.j9360.com/article/265500.htm實現方式一:可以在模塊頂部將所有寄存器引出,提供統一的模塊進行配置和讀出。這種方式簡單是簡單,但是頂層連接工作量較大,并且如果配置個數較多,導致頂層中寄存器的數目也會較多。

實現方式二:通過總線進行連接,為每個模塊分配一個地址范圍。這樣寄存器等擴展就可以在模塊內部進行擴展,而不用再頂層進行過多的頂層互聯。如下圖所示:

那如果進行總線的選擇,那么有一種極為簡單的總線推薦被使用,那就是AVALON-MM的總線

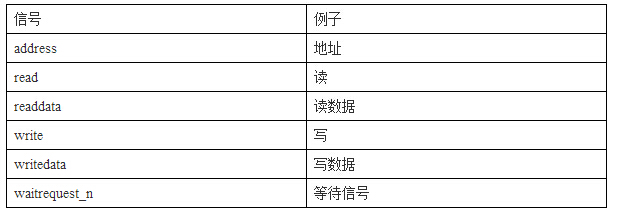

ALTERA提出兩種總線類型,分別是AVALON-MM, AVALON-ST。分別用于連接memeory 和數據流的傳送 MM不是你想的意思,其英文為memory map。實現內存映射是其主要目的。主要信號包括如下表所示:

AVALON-MM因此可以說是最簡單實用的總線形態了。對于其操作來說,總線為同步類型的總線,寫信號只需要在寫使能有效時,同時提供寫數據即可,而讀數據等待信號無效時,讀出數據有效。

同樣數據類型讀數據(readdata)和寫數據(writedata)的寬度可以根據設計的需要靈活配置為(8,16,32----256---1024)BIT等值。即可以支持非常大的位寬,但普通應用,只需要(8,16,32,64)BIT等即可滿足應用。

那假設總線寬度32,基本上主流的數據總線的寬度。如果需要更細粒度的劃分,確定讀寫某個字節有效,那么byteenable信號也是必須的。其需要4bit來標示32bit(4個byte)中那個有效,每一BIT表示一個字節,因此如果要完全表示所有的字節有效,因此字節有效信號的寬度為(數據總線的寬度/8)。AVALON還可以有burst的操作。主設備可以通過burstcount設備確定brust的長度,為2的n-1次方。

對于普通的應用,通過上述表格中的基本操作即可滿足需求,這也正是AVALON-mm總線的優勢。此外模塊按此標準提供連接接口,各種模塊可以掛在NIOSII的片上系統上。

如果模塊之間為點對點的連接,同時傳遞大數據量的操作,那么的AVALON-mm總線就不太適合,因此AVALON_streaming總線就適合這種應用場景。

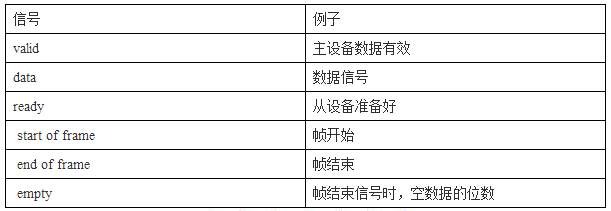

AVALON_streaming總線本質上是一種同步并行總線,即在同步時鐘狀態下,使能有效代表傳遞數據有效。其基本信號如下表所示:

從上圖中,可以看出各信號在數據傳輸中的作用,對于從設備獲取數據的處理,就是VALID有效時,數據有效的采樣操作,非常簡單方便,易于處理。如果從設備設定ready永為1,則表示沒有反壓的機制,則主設備,可根據自身收包情況一直向從設備發送數據包。此外還有其他輔助信號,可以根據設計需要進行添加。

使用總線使模塊標準化,便于代碼的移植和設計復用。同時標準總線的設定和統一定義也利于項目團隊代碼的標準化,便于理解和傳播。

下文將介紹兩種其他應用較廣的總線形態,AHB(AMBA) 和WISHBONE總線(待續)。

評論