基于FPGA的機載顯示系統架構設計與優化

⑦ 視頻旋轉模塊寫數據,由于視頻處理速度和圖形處理速度不完全匹配,所以先將縮放及旋轉后的數據存儲到DDR3,等待圖形處理完后,再統一取出,讀寫數據量為237.3 MB/s。

本文引用地址:http://www.j9360.com/article/264924.htm⑧ 視頻輸出讀數據,同時進行平移、翻轉、鏡像等坐標變換操作,讀寫數據量為237.3 MB/s 。

⑨ 預畸變參數讀數據,用64位來存儲每個像素點對應的四個預畸變參數,則讀數據量為

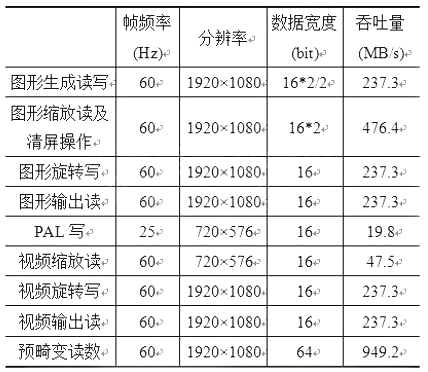

表1為該系統數據吞吐量的計算表,其吞吐量合計為2677.6 MB/s 。

表1系統數據吞吐量計算表

本文采用DDR3作為系統外部存儲器,其型號為W3H128M72E,數據寬度為72比特(64比特為數據位,8比特為校正位),采用的時鐘為400MHz,由于DDR3在上升沿和下降沿都進行數據的讀寫操作,等效于其內部讀寫時鐘為800MHz,即數據帶寬為6400MB/s(800MHz*64bit),滿足本文設計系統的數據吞吐量要求。

3 機載顯示系統架構優化

設計的機載顯示系統架構能夠滿足性能要求,但是還需要進一步優化。如圖 5所示,改變不同模塊之間的順序來優化設計,同時改進算法。具體改變如下:

① 圖形整體相對于屏幕的縮放和旋轉功能在CPU端發送命令前實現,因為CPU端旋轉和縮放是針對頂點進行的,方便快速,同時減少了FPGA的BRAM資源占用,減少了進出DDR3的次數;

② 改進幀速率提升算法,進一步減少延遲,提高實時性;

③ 改進視頻旋轉算法,進一步降低緩存區的大小,減少BRAM的占用率;

④ 幀速率提升和平移、翻轉、鏡像都需要通過讀寫DDR3來完成,將兩者合并,同時完成,減少進出DDR3的次數。

圖5 FPGA邏輯優化的整體流程圖

3.1 實時性分析

實時性是機載顯示系統重要的衡量標準之一,為了確保飛機運行安全,必須確保視頻處理的各個模塊都有較高的實時性。視頻采集、視頻縮放、視頻校正、視頻輸出延遲都是幾行,延遲時間在 以內。幀速率提升模塊的延遲遠大于其他各個模塊延遲之和,需要進一步改進,在保證顯示質量的同時,進一步降低延遲時間。

3.1.1 幀速率提升算法優化

改進的幀速率提升算法仍使用幀復制法。在DDR3中開辟4個存儲空間做切換用于存放幀速率為25Hz、場速率為50Hz的PAL圖像。有4個場緩存區,當接收當前幀的奇場后與前一幀的偶場結合成一幀數據輸出。

幀速率改進算法示意圖如圖 6所示。A場正好寫完,B場正好讀完,下一幀讀取A場數據,這樣延遲為PAL的1場(半幀);A場正好還差1行寫完,B場已讀完,下一幀繼續讀B場,這樣延遲為PAL的1+(25/60)=1.42場。延遲為PAL的1~1.42場。最大延遲為。

圖6 幀速率改進算法示意圖

3.2 BRAM資源占用

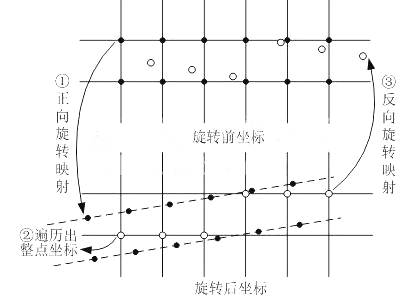

原設計的機載顯示系統架構使用反向映射的方法實現旋轉算法,每一行旋轉后數據反向旋轉時需要緩存334行視頻旋轉前數據,即需要279個36Kb的BRAM。相對于其它模塊緩存幾行相比,占用了大量的BRAM空間,因此需要改進。

3.2.1 視頻旋轉算法優化

視頻旋轉提出了一種改進的旋轉映射法,降低緩存空間。示意圖如圖 7所示。對以行掃描的方式獲取的視頻圖像,緩存兩行就能開始旋轉處理,先進行正向映射,根據當前兩行對應的旋轉后浮點坐標,找到兩行內的整點坐標,再對其進行反向映射,利用當前兩行來得到旋轉后整點坐標的像素值。

圖7 視頻旋轉改進算法示意圖

該算法涉及原始圖像中的2*2大小鄰域,為了提高該模塊的處理速度,設計了一組由三個雙端口塊存儲器BRAM組成的原始圖像數據緩存器。每個BRAM用來存儲1行原始圖像的數據,3個BRAM中存儲的原始圖像數據包括當前旋轉計算涉及的兩行原始圖像數據以及下一行旋轉計算涉及的一行原始圖像數據。因此,需要緩存3行,使用3個36Kb的BRAM。

3.3 DDR3吞吐量分析

從圖5可以看出,優化后的系統流程最多經過DDR3共5次,下面依次介紹每次讀寫DDR3的必要性和數據量。

① 圖形及字符生成模塊讀寫數據,此與原模塊相同,則圖形生成模塊讀寫數據量為

② 圖形輸出模塊讀數據及清屏操作寫數據,由于視頻輸出模塊是對整個畫面的處理,所以需要從DDR3中讀取出來,而由于圖形及字符不是對每個像素點都進行操作的,所以取出后,需要進行清屏操作。則讀寫數據量為474.6 MB/s 。

③ 視頻旋轉寫數據,旋轉后的數據沒有嚴格按照屏幕自上而下的順序,必須將數據存儲到DDR3中進行變換操作,讀寫數據量為

④ 視頻輸出模塊讀數據,從DDR3中取出進行視頻輸出操作,取出的同時還能進行一些坐標變換操作,如平移、翻轉、鏡像等,讀寫數據量為

⑤ 預畸變參數讀數據,用64位來存儲每個像素點對應的四個預畸變參數,則讀寫數據量為

表 2為該系統數據吞吐量的計算表,其吞吐量合計為2135.7MB/s。DDR3的數據帶寬為6400MB/s(800MHz*64bit),滿足本文設計系統的數據吞吐量要求。

表2 優化后系統數據吞吐量計算表

結論

本文設計一種基于FPGA的機載顯示系統架構,能夠實現2D圖形繪制,構成各種飛行參數畫面,同時疊加外景視頻圖像。實時性方面,幀速率提升模塊延遲最大為;BRAM資源占用方面,視頻旋轉算法需要279個36Kb的BRAM;DDR3吞吐量方面,系統吞吐量為2677.6 MB/s。

優化后的機載顯示系統,實時性方面,幀速率提升模塊延遲最大為;BRAM資源占用方面,視頻旋轉算法需要3個36Kb的BRAM;DDR3吞吐量方面,吞吐量為2135.7 MB/s。

經過對比分析,優化后的機載顯示系統實時性提高、BRAM資源占用減少、吞吐量降低,整體性能得到了提升。

fpga相關文章:fpga是什么

評論