基于FPGA的簡易頻譜分析儀

1 引言

本文引用地址:http://www.j9360.com/article/264346.htm目前,由于頻譜分析儀價格昂貴,高等院校只是少數實驗室配有頻譜儀。但電子信息類教學,如果沒有頻譜儀輔助觀察,學生只能從書本中抽象理解信號特征,嚴重影響教學實驗效果。

針對這種現狀提出一種基于FPGA的簡易頻譜分析儀設計方案,其優點是成本低,性能指標滿足教學實驗所要求的檢測信號范圍。

2 設計方案

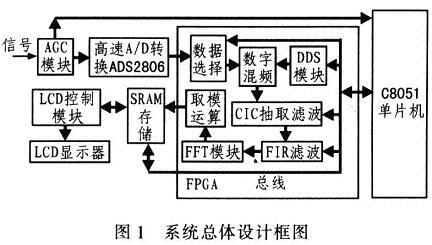

圖1為系統設計總體框圖。該系統采用C8051系列單片機中的 C8051F121作為控制器,CvcloneⅢ系列EP3C40F484C8型FPGA為數字信號算法處理單元。系統設計遵循抽樣定理,在時域內截取一段適當長度信號,對其信號抽樣量化,按照具體的步驟求取信號的頻譜,并在LCD上顯示信號的頻譜,同時提供友好的人機會話功能。該系統最小分辨率為1 Hz,可分析帶寬為0~5 MHz的各種信號。

由于單片機C8051 F121內部集成A/D轉換器,能夠有效測量自動增益控制AGC壓差,計算出對輸入信號的放大倍數;另外,該單片機內置高速控制內核和豐富的存儲器,使其能夠控制整個系統;EP3C40F484C8型FPGA內置豐富的存儲器資源,確保該系統具有足夠的空間存儲采集的點數,完成離散傅里葉變換、數字濾波器、數字混頻等信號處理。

3 理論分析

3.1 數字下變頻FFT

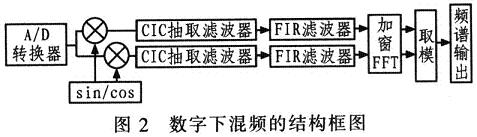

隨著高速A/D轉換和DSP技術的發展,數字下變頻的快速傅里葉變換FFT(Fast Fourier Transform)技術能夠有效減少傳統FFT技術存在的內存不足。在高中頻、高采樣率系統中實現信號頻譜的高分辨率、低存儲量和低運算量,從而極大提高系統的實時性。

圖2為基于數字下變頻的FFT技術的實現原理框圖。

3.2 直接數字頻率合成器DDS原理

用直接數字頻率合成器DDS(Direct Digital Synthesiz-er)原理實現掃頻信號的信號源主要由參考頻率源、相位累加器、正弦波采樣點存儲RAM、數模轉換器及低通濾波器構成。設參考頻率源頻率為fclk,計數容量為2N的相位累加器(N為相位累加器的位數),若頻率控制字為M,則DDS系統輸出信號的頻率為fout=fclk/2N×M,而頻率分辨率為△f=fclk/2N。為達到輸出頻率范圍為5 MHz的要求,考慮到實際低通濾波器性能的限制,fclk為200 MHz,相位累加器的位數為32位。其中高10位用做ROM地址讀波表(1個正弦波周期采樣1 024個點),頻率控制字也為32位,這樣理論輸出頻率滿足要求。

4 系統硬件設計

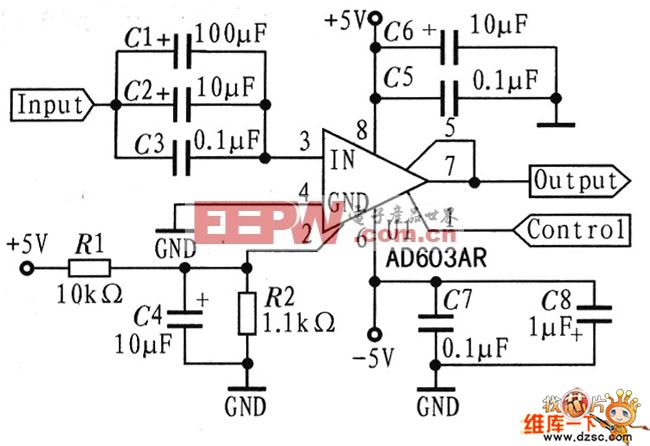

4.1 AGC電路

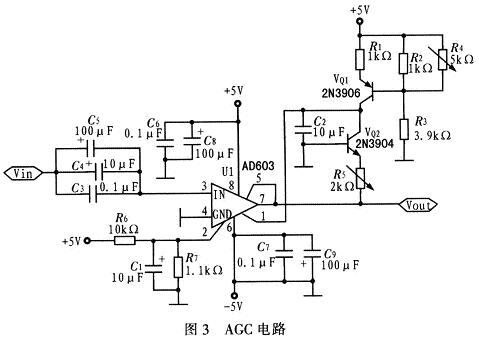

輸入信號經高速A/D采樣,信號幅度必須滿足A/D的采樣范圍,最高為2-3V,因此該系統設計應加AGC電路。AGC電路采用AD603型線性增益放大器。圖3為AGC電路。

4.2 A/D轉換電路

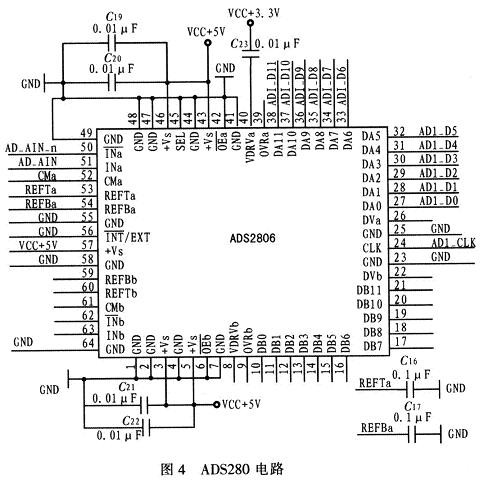

ADS2806是一款12位A/D轉換器,其特點為:無雜散信號動態范圍(SFDR)為73 dB;信噪比(SNR)為66 dB;具有內部和外部參考時鐘;采樣速率為32 MS/s。圖4為ADS2806的電路。為使A/D轉換更穩定,在A/D轉換器的電源引腳上增加濾波電容,抑制電源噪聲。該電路結構簡單,在時鐘CLK的驅動下,數據端口實時輸出數據,供FPGA讀取。

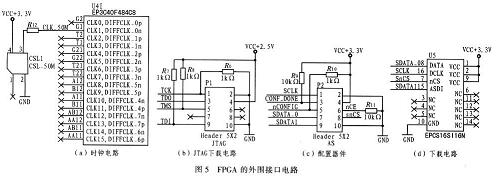

4.3 FPGA及外圍接口模塊

選用CycloneⅢ系列EP3C40F484型FPGA,該器件內部有39 600個LE資源,有1 134 000 bit的存儲器,同時還有126個乘法器和4個PLL鎖相環。由于該器件內部有大量資源,因而可滿足其內部實現數字混頻、數字濾波、以及FFT運算。FP -GA正常工作時,主要需要的外部接口有:時鐘電路、JTAG下載電路、配置器件及下載電路。圖5為FPGA的外圍接口電路。

5 系統軟件設計

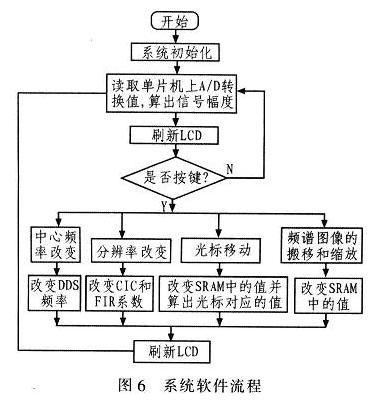

系統軟件設計包括單片機和FPGA兩部分,單片機作為整個系統的核心控制單元,主要負責系統的初始化、鍵盤輸入控制以及LCD顯示等功能;而FPGA的高速并行計算性能使其很適合進行實時性要求較高的信號處理運算。系統軟件流程如圖6所示。

系統上電后,單片機分別初始化系統各個模塊,寫入默認的CIC、FIR濾波器參數和寫入默認的數字混頻器頻率值。初始化完成后,系統開始以默認的中心頻率和分辨率分析頻譜,進入等待鍵盤輸入狀態。當用戶通過鍵盤重新輸人中心頻率和分辨率等參數后,單片機重新刷新LCD,同時可通過鍵盤操作LCD上的畫面,移動光標,利用軟件計算對應光標處的頻率值并在LCD上顯示,而且還可以對整個圖像進行放縮以方便觀察頻譜。

6 測量結果分析

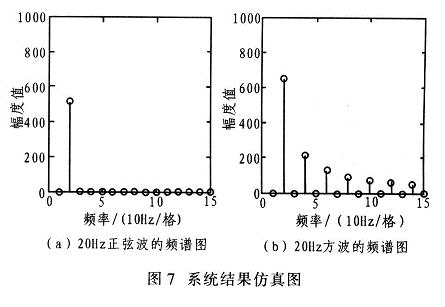

先通過Matlab軟件進行仿真,分別用程序測試頻率為20 Hz的正弦波方波,系統仿真結果如圖7所示。從圖7a看出20 Hz正弦波頻譜是一條譜線,其周圍只有很少泄漏頻率分量,符合理想情況。圖7b是20 Hz方波的分析結果,其基波,第三、第五、第七次諧波的幅度滿足1、1/3、1/5、1/7、1,9的理論結果。

7 結束語

該系統能夠方便地在LCD上顯示信號的頻譜結構圖。操作簡單,便于學生進行操作,有助于實驗教學課上學生更直觀認識信號頻譜結構,從而促進實驗課教學。

fpga相關文章:fpga是什么

低通濾波器相關文章:低通濾波器原理

混頻器相關文章:混頻器原理 數字濾波器相關文章:數字濾波器原理 鎖相環相關文章:鎖相環原理 汽車防盜機相關文章:汽車防盜機原理 頻譜分析儀相關文章:頻譜分析儀原理

評論