基于FPDP和VME總線的多DSP通用并行處理系統設計方案

引言

本文引用地址:http://www.j9360.com/article/257533.htm基于TIDSP數字信號處理器的通用信號處理板在聲納、雷達信號處理中已經有著廣泛的應用。但在一些實時性要求很高的場合,單板多DSP系統并不能完成高速的數據采集傳輸和大量的數據分析處理工作,從而需要一個由信號采集板和信號處理板組成的多子板系統實現高速實時處理。借助多板多DSP并行處理技術,能夠開放性地實現實時性強、精度高、動態范圍大和高數據吞吐量連接網絡的大規模并行處理系統。此時,數據的板間傳輸成為這些系統的設計瓶頸。

本文將介紹一種基于FPDP和VME雙總線的高速實時信號處理結構可重組多子板系統,并著重分析該系統核心子板——多DSP通用并行處理系統的硬件設計和原理框圖。

2、多子板系統總體設計

2.1 系統結構分析

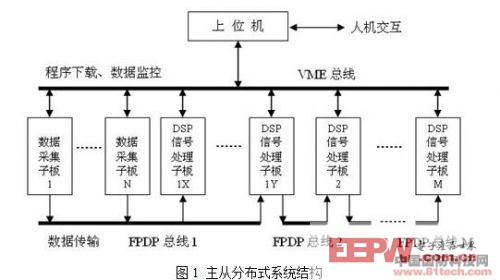

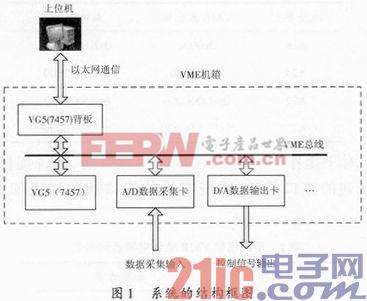

本系統是依托于標準VME機箱的高速實時信號處理結構可重組多子板系統。它由上位機、下位機和VME機箱構成。結構框圖如圖1所示,它具有以下5個特點:

1.上位機為工控機,下位機由多塊數據采集板和DSP信號處理板組成。

2.DSP信號處理板采用一主三從的多DSP并行處理結構。

3.每個下位機都通過標準的總線接口與上位機相連,上位機對下位機起主導作用,它可以通過公共總線下載或更新下位機上的DSP、FPGA等處理器程序,并且隨時監控數據。

4.各子板之間數據通過專門的總線傳輸,不通過上位機統一分配調度。

5.系統結構靈活多變,具有一定可重組性。系統各類子板都做了可擴展性設計。

系統結構可重組性主要解決數據采集通道擴展和信號處理算法多樣性等各類問題。系統結構可重組性表現為一方面數據采集可選用單通道結構或者多通道結構,另一方面DSP子板可根據所實現的信號處理算法性能和各通道采集數據的數量及相關性而組合多板串行分步處理結構或者多板獨立并行處理結構。

在圖1中,系統除去DSP1X等板,保留DSP1Y、2……M板的結構是多板串行分步處理結構:各通道數據通過數據傳輸總線依次傳送至DSP1Y板進行第一步處理,DSP1Y板然后將運算結果傳送至DSP2板進行下一步處理,以此類推直至完成各步處理得出最終結果。相反,系統除去DSP2……M板,保留DSP1X……1Y板的結構便是多板獨立并行處理結構:各通道數據通過同一數據總線依次或者不同總線同時傳至各自相對應的DSP1X……1Y板進行獨立并行處理。當然在數據量極大或者算法極其復雜的情況下,我們還可以將系統重組成串行和并行混合處理的結構。

VME總線是軍用標準總線的主流類型,其技術成熟可靠,發展時間長,廣泛應用于水下通信、雷達聲納、軟件無線電等領域。基于DSP程序下載和數據監控的高穩定性要求,我們在系統中采用VME總線實現上位機與下位機的板間通訊。下位機之間的通訊主要涉及到的是數據傳輸。VME總線對于此類傳輸就具有協議復雜,調試困難以及速度慢等弱點。因此我們采用目前通用的高速數據傳輸總線FPDP實現下位機之間通訊。

FPDP(front panel data port)前面板數據口協議是由VITA Standards Organization提出的。基于最小等待時間與精確傳輸速率,FPDP總線用于在兩個或多個VME總線子板之間提供高速數據傳輸,總線寬度為32bit,通過80線帶狀電纜連接。單一發送設備,沒有總線沖突,協議不包含地址和仲裁周期。數據傳輸速率完全由發送設備的時鐘決定,TTL時鐘strobe頻率最高為20MHz,±PECL data strobe的頻率最高為40MHz,因此數據傳輸最大帶寬為160MB/S。

基于FPDP總線的高速數據板間傳輸設計實現分為信號發送和信號接收兩部分。它包括FPDP主發送端(FPDP/TM)、發送端(FPDP/T)、FPDP主接收端(FPDP/RM)和接收端(FPDP/R)。FPDP總線可擴展為一個主發送端、多個發送端和一個主接收端、多個接收端的形式。這種可擴展傳輸結構完全符合本文介紹的高速信號處理系統各種結構下多種數據傳輸方式要求。如圖1所示,在系統中,子板通訊采用多條FPDP總線。數據采集板只設計有FPDP/TM接口,主要負責各通道數據采集發送。DSP信號處理板同時設計有FPDP/TM和FPDP/RM接口,配合系統結構重組。系統處于多板獨立并行處理結構時,DSP板啟動RM模塊,只做數據接收終端。系統處于多板串行結構時,前板的FPDP/TM與后板的FPDP/RM相接,構成獨立的FPDP總線,從而配合多個DSP板流水作業。在多通道或者多板并行處理結構中,每個FPDP總線上,必須且只能設定一個主接收端和一個主發送端。

在系統中我們可以通過硬件編程、開關和軟件修改對FPDP/TM、FPDP/RM進行配置,實現各個系統結構中數據實時多向傳輸。

評論