DSP虛擬I2C總線軟件包的設計

3.2 X1203的讀寫操作

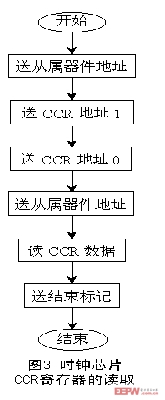

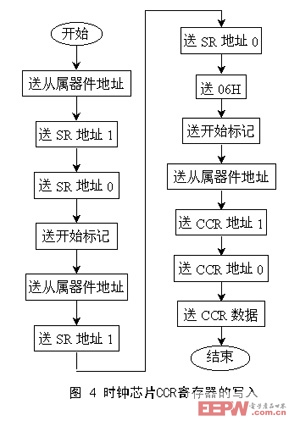

這里僅給出F206對X1203進行讀寫的基本流程,如圖3、圖4所示,分別為對時鐘芯片的讀、寫過程。其中進行寄存器寫時,須注意SR寄存器中WEL和RWEL的設置是否正確,即首先設置WEL有效,而后將WEL、RWEL都置1,否則數據將不能正確寫入。在寫結束后,應將WEL、RWEL置為無效,以免產生誤操作。

此外還須指出,在系統首次上電后(VBack和VCC都失效后),至少有一字節寫入RTC寄存器時,系統才開始工作。在實際使用中,應首先判斷SR中的RTCF位是否為1,若是,表明系統為首次使用或VBack和VCC都已失效,須對X1203至少進行一次寫入操作,使其正常計數。

時鐘芯片讀寫子程序清單如下:

.copy init.h

.copy vector.h

;以下為I2C軟件包中的符號定義

VSDA .set 0008h

VSCL .set 0004h

RAM0 .set 60h

SLA .set 61h

RIO .set 62h

NUMBYTE .set 63h

MTD .set 0100h

MRD .set 0120h

setc intm ;關中斷

clrc cnf ;映射塊 B0 到數據存儲區

ldp #0h ;頁指針設置為0

clrc sxm

;數據寫入使能程序段

splk #0deh,SLA

splk #3,NUMBYTE

lar ar0,#MTD

mar *,ar0

splk #0,*+

splk #03fh,*+

splk #02h,*+

call wrnbyte

splk #0deh,SLA

splk #3,NUMBYTE

lar ar0,#MTD

mar *,ar0

splk #0,*+

splk #03fh,*+

splk #06h,*+

call wrnbyte

;寫入數據程序段

splk #0deh,SLA

splk #9,NUMBYTE

lar ar0,#MTD

mar *,ar0

splk #0,*+

splk #030h,*+

splk #01h,*+

splk #02h,*+

splk #03h,*+

splk #03h,*+

splk #02h,*+

splk #01h,*+

splk #21h,*+

call wrnbyte

;禁止數據寫入程序段

splk #0deh,SLA

splk #3,NUMBYTE

lar ar0,#MTD

mar *,ar0

splk #0,*+

splk #03fh,*+

splk #0h,*+

call wrnbyte

;數據讀取程序段

splk #0deh,SLA

splk #2,NUMBYTE

lar ar0,#MTD

mar *,ar0

splk #0,*+

splk #030h,*+

call wrnbyte

splk #0dfh,SLA

splk #7,NUMBYTE

call rdnbyte

wait: b wait

結束語

I2C總線應用已日益廣泛,而其協議的復雜性和操作的特殊性又限制了推廣速度。本文介紹的一種基于DSP的虛擬I2C總線軟件包,簡化了TMS320C2XX與I2C器件間接口程序設計,用戶無需了解I2C總線協議的細節,僅需通過唯一的接口界面wrnbyte/ rdnbyte即可實現相應的接口。本文還給出了一個TMS320F206與時鐘芯片X1203間的接口實例,介紹了軟件包的使用方法,希望能供讀者參考。

評論